1. 소개

목표

- 컴퓨터가 어떻게 동작하는지

- 문제를 어떻게 처리하는지

- 하드웨어와 소프트웨어를 어떻게 개발하는지

객체 지향 언어로 작성한 코드 예시

(아래는 이 책에서 구현하는 Jack이라는 언어를 사용)

class Main {

function void main(){

do Output.printString("Hello World");

do Output.println(); //new string

return;

}

}

코드

- 텍스트 파일에 저장된 문자들

어떻게 프로그램이 동작할까?

1. 코드를 파싱

2. 의미를 분석

3. 컴퓨터가 이해하는 저급 언어로 변환

기계어

- 2진법으로 구성된 추상적인 언어

- 기계어로 코딩하려면 하드웨어 아키텍처에 대해 알아야 함

하드웨어 아키텍처

- 레지스터, 메모리, ALU 등 하드웨어 장치들로 구성

하드웨어 장치

- 위 하드웨어 장치들은 논리 게이트로 만들어짐.

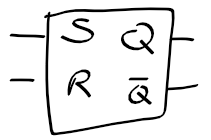

논리 게이트

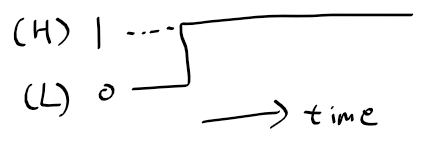

- AND, NOT, OR, NAND, NOR 등

스위치 회로

- 하드웨어 구성에 필요한 스위치에 트랜지스터를 사용

우리가 그동안 배운 컴퓨터 시스템은 빙산의 일각이며,

아래의 내용들을 이해해서 프로그램 코딩 구현 뿐만이아니라 하드웨어와 소프트웨어를 다룰수 있게 됨.

=> 이 기술들을 이해할 수 있도록 밑바닥 부터 컴퓨터를 만들어 보자

컴퓨터

- 논리 게이트로 만들 수 있음.

모듈

- 매우 복잡하니 모듈이란 개념으로 분리해서 다룸

추상화

- 예술과 과학 분야 에서 자주 사용

- 생각이나 특정 개채를 분리하기 위한 개념

컴퓨터 과학에서 추상화

- 매우 많이 쓰임

- 이 개체가 뭘하는건지를 의미함

- 어떻게 동작하는지 세부적인건 X

=> 사용자들은 어떻게 만들어지는지 몰라도 되고 쓰는 법만 알면 됨.

개발자의 추상화

- 하드웨어/소프트웨어 개발자는 인터페이스라 부르는 추상화 작업을 자주 해야함

- 추상화를 한 층 한층하면서 상위 레벨로 올라가 다양한 역활을 하게 됨

컴퓨터 시스템 설계 추상화

- 탑다운 방식으로 나타낼 수 있음.

-> 고 레벨 추상화를 단순화

- 바텀 업으로 나타 낼 수 있음

->저 래밸 추상화를 모아 복잡하게 상위로

탑 다운으로 보는 학습 내용

- 고급 언어

- 고급 언어 ~ 하드웨어

-> 고급 언어를 기계어로 변환 과정

-하드웨어 플랫폼

고급언어

개발자가 개발시 필요한 것

- 고급 언어와 라이브러리

예시 do Output.printString("Hello world").

위 코드의 경우 문자열 출력(printString)을 하기위해 이미 구현된 라이브러리를 사용함.

=> OS와 표준 언어 라이브러리가 필요

표준 언어 라이브러리는 뭐고, 운영 체제가 어떻게 동작할까?

- 수학 관련 함수

- 메모리 할당 함수

- 입출력 루틴

- 문자열 처리 등이 사용됨.

잭(Jack)

- C언어 비슷한 객체지향 언어

고급언어 ~ 하드웨어

- 프로그램을 실행하려면 동작하는 컴퓨터 플랫폼(타겟 컴퓨터)의 기계어로 변환해야함

-> 컴파일

컴파일

- 여러 추상화 레이어로 나눌 수 있음

- 컴파일러, 가상 머신, 어셈블러

컴파일러가 하는일

- 컴파일러의 변환 작업은 문법 분석과 코드 생성을 수행함.

- syntax analysis : 소스 코드를 분석해서 의미 단위들을 파스 트리(parse tree)라는 데이터 구조로 나눔.

- 파스 트리를 재귀적으로 처리해서 중간 코드 생성

중간 코드(Intermdeiate Code)

- 소스 코드를 표현하기 위해 컴파일러나 가상머신에서 내부적으로 사용하는 코드

가상 머신(Virtual Machine)

- 스택 구조

- 컴파일러에서 생성한 중간 코드를 어셈블리 프로그램으로 변환

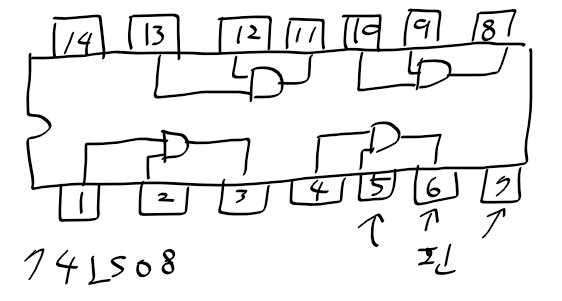

어셈블러

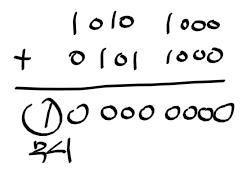

- 어셈블리어로 된 프로그램을 이진 코드로 변환

하드웨어

Hack

- 4시간 만에 만들수 있는 컴퓨터 아키텍처

- 단순하면서도 성능있음.

- 하드웨어 요소로 어떻게 디지털 컴퓨터 설계하는 과정을 이해하는데 사용함.

HDL

- Hardware Description Language(HDL)

- 이 언어로 하드웨어 시뮬레이션하여 Hack을 만듬.

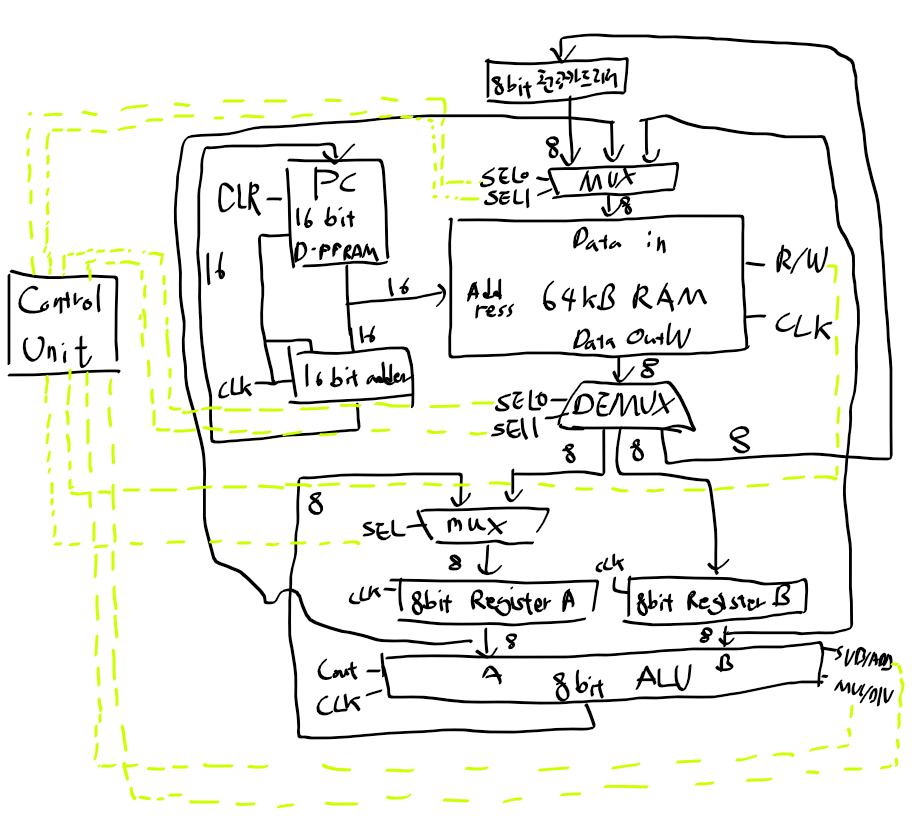

Hack 컴퓨터

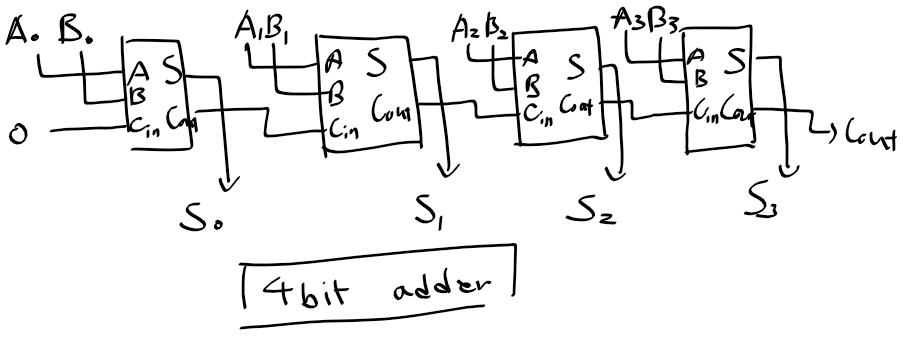

- 구성 : CPU, RAM, ROM, 시뮬레이션 스크린, 키보드 등

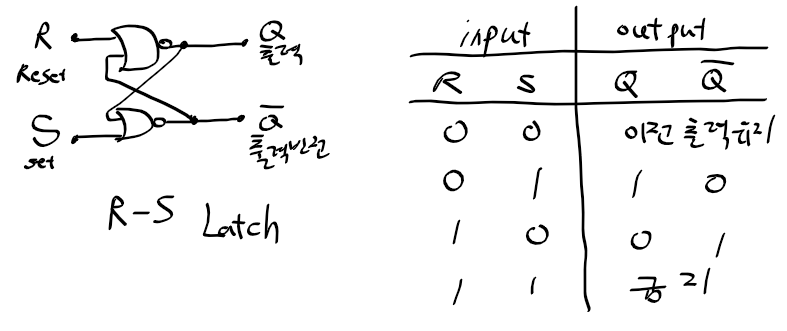

- 이 컴퓨터는 논리 게이트를 조합해서 만들며 부울 대수를 따라 동작함.

논리 게이트

- 트랜지스터로 만듬.

'컴퓨터과학 > 컴퓨터, OS' 카테고리의 다른 글

| Nand2Tetris 2 - 불 연산 (0) | 2020.04.29 |

|---|---|

| NAND2Tetris 1 - 불 논리 (0) | 2020.04.25 |

| 기계어~OPCODE (0) | 2020.04.25 |

| ALU~보조기억장치 (0) | 2020.04.24 |

| 가산기~주기억장치 (0) | 2020.04.24 |