모든 디지털 장비

- 컴퓨터, 폰, 라우터 등 정보 저장하고 처리하는거 전부다

- 칩 구성은 다 다르지만. 논리 게이트로 만들어짐

논리 게이트

- 다른 물질로 만들거나 만드는 방법은 다르더라도 모든 컴퓨터에서 똑같이 논리 연산을 수행

- NAND를 주로 사용

불 게이트(Boolean gate)

- 부울 함수를 따름.

부울 대수(Boolean Algebra)

- 부울 대수는 Boolean(이진) 값을 처리함

- 2진 입력을 받아 2진 출력을 보냄

진리표(Truth Table)

- 입력에 대한 부울 연산 결과를 들을 보여 줌

기본 부울 연산자(boolean operator)

- And, Or, Not

AND(논리 곱)

- 둘다 1이면 1

OR(논리 합)

- 둘중 하나면 1이면 1

NOT(부정)

- 1이 입력되면 0, 0이 입력되면 1 -> 반전

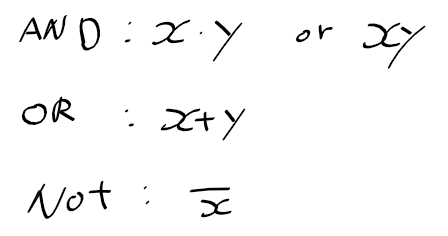

기본 부울 연산의 수학적 표현

불 함수

- 부울 연산자를 조합한 함수

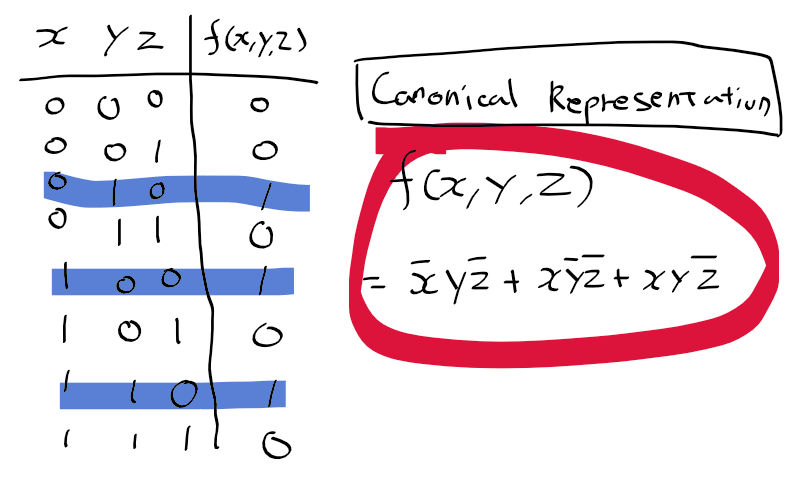

불 함수의 예시와 진리표

표준 형식(Canonical Representation)

- 위 불 함수의 경우 1인 경우들만 모아 다음의 표준 형식으로 정리할 수 있음.

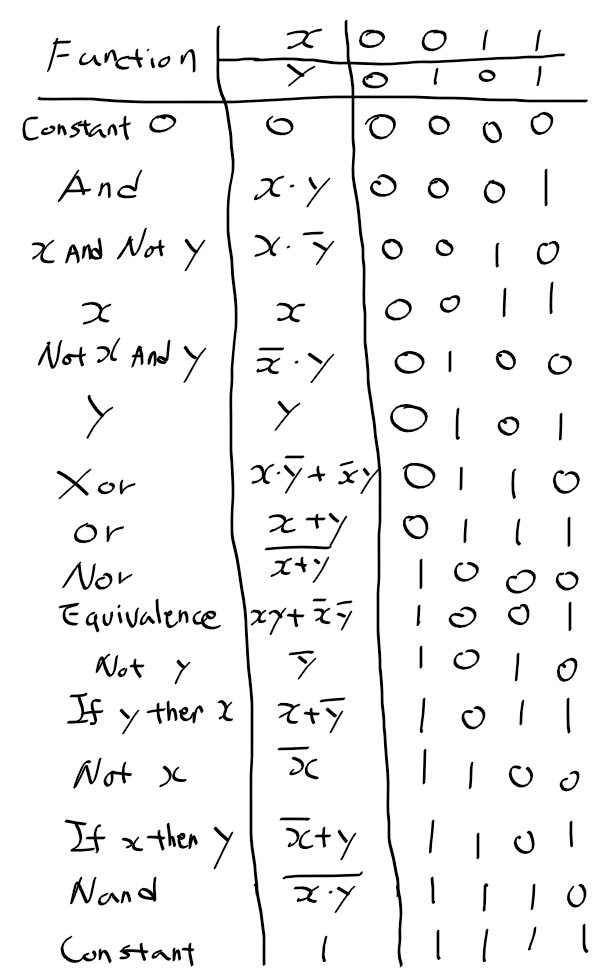

2입력 부울 함수 정리

논리 게이트

- 게이트는 부울 함수를 물리적으로 구현한 장치

- 스위치 역활을 하는 트랜지스터로 만들어짐

기본 논리 게이트

조합 논리 게이트

- 기본 논리 게이트를 조합하여 만들 수 있음.

하드웨어 기술 언어

- HDL(Hardware Description Langauge) = VHDL(Virtual HDL)

- 하드웨어 설계자들은 실제 게이트를 조립하지 않고 HDL로 설계함.

- HDL 프로그램을 시뮬레이션에 입력하여 결과를 구함.

Xor 게이트 만들기

- Xor(a,b) = Or(And(a,Not(b)), And(Not(A),B))

HDL 작성하기

- HDL 칩 정의는 헤더와 파츠 부분으로 나뉨

- 헤더는 칩 인터페이스를 정의 -> 칩의 이름과 입력 출력 핀

- 파츠에서는 저수준 파츠의 구성과 이름 등을 정의함.

Vscode Nand2Tetris 하이라이팅 설치

- VScode에서 Nand2Tetris를 위한 문법 하이라이팅 제공하고 있다.

Xor 게이트 구현

- Xor.hdl : 헤더에 Xor 게이트 칩 인터페이스 정의, Parts 섹션에 파츠 연결관계 정리

- Xor.tst : 하드웨어 시뮬레이터에서 사용할 테스트 데이터

- Xor.out : Xor.tst에 따라 시뮬레이션 테스트 결과

Nand2Tetris 하드웨어 시뮬레이션 수행 결과

NAND Gate 구현 및 실험

먹스(Multiplexor)

- 입력 : a, b 입력과 둘중 하나를 출력으로 보내는 선택 비트 3개로 이루어짐

- 먹스 진리표에 따라 회로를 다음과 같이 정리 할 수 있음.

먹스 시뮬레이션

디먹스(DeMultiplexor)

- 입력으로 in과 sel을 받아 sel이 0이면 a, sel이 1이면 b로 보내는회로

디먹스 시뮬레이션

16비트 Not

And16

Or16

Mux16

Or8way

Mux4way16

- 우선 4-way-mux 구현

- 이후 4-way-mux 16개를 이음

Mux8way16

- 우선 8-way-mux 구현

- 이후 8-way-mux 16개를 이음

* 이 코드는 동작은 잘하는데 문제는 너무 길다. 다른사람들이 한걸 보니 MUX16을 구현 후 4 입력을 처리해주더라..

DMux4Way

DMux8Way

'컴퓨터과학 > 컴퓨터, OS' 카테고리의 다른 글

| 주소 지정방식 (0) | 2020.04.29 |

|---|---|

| Nand2Tetris 2 - 불 연산 (0) | 2020.04.29 |

| NAND2Tetris 0 - 소개 (0) | 2020.04.25 |

| 기계어~OPCODE (0) | 2020.04.25 |

| ALU~보조기억장치 (0) | 2020.04.24 |