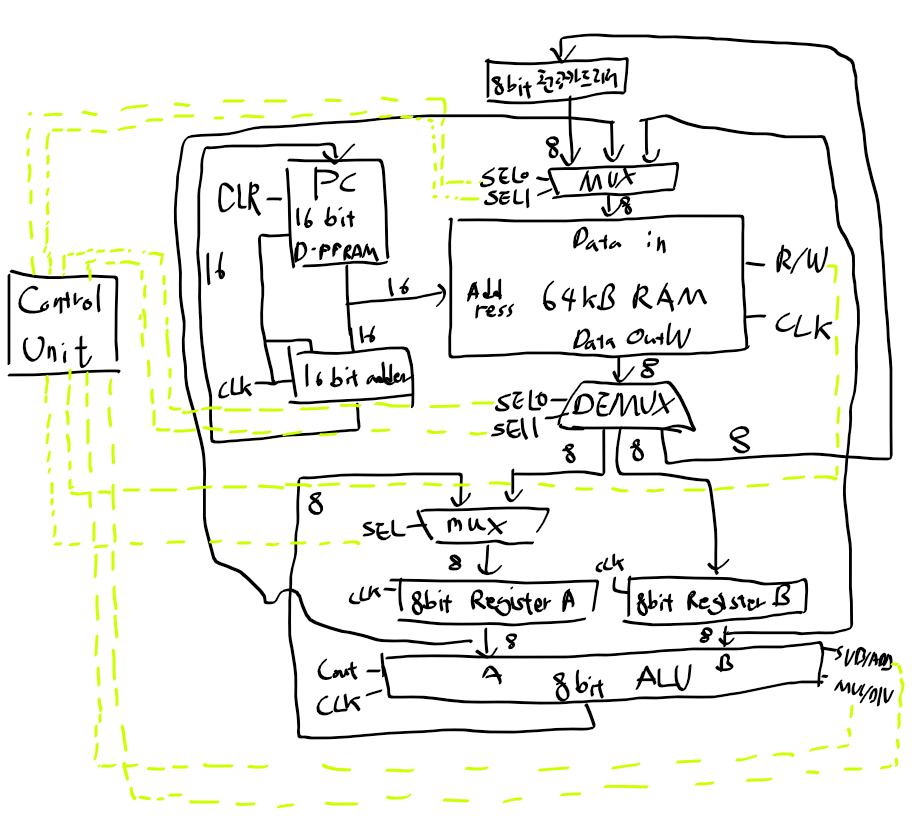

제어기

- 컴퓨터회로의 멀티플렉서, 디멀티플렉서, ALU의 ADD/SUB 등 제어가 필요한 부분들이 존재

- 한 곳으로 모은 제어기를 만듬

제어기 스위치

- 제어기 스위치를 제어하여 로드/스토어 작업 수행

제어 예시

- PC가 가리키는 SRAM 값을 레지스터 A에 저장

- SRAM MUX SEL : 0 0[보조 기억장치 선택]

- SRAM DEMUX SEL : 0 0 [레지스터 A 방향 선택]

- Reg A MUX SEL : 1[SRAM 방향 선택]

- SRAM RW : 1[읽기 모드]

- MUL/DIV : 0[상관 x]

- SUB/ADD : 0[상관 x]

-> 레지스터 A에 값을 저장 = 00001100 = 0x0C

MUX/DIV와 SUB/ADD 조합에 따른 ALU의 연산

* 덧셈 : 0(MUL/DIV), 0(SUB/ADD)

* 뺼셈 : 0(MUL/DIV), 1(SUB/ADD)

* 곱셈 : 1(MUL/DIV), 0(SUB/ADD)

* 나눗셈 : 1(MUL/DIV), 1(SUB/ADD)

기계어

- 컴퓨터 회로의 제어기를 제어하는 2진수 언어

위 컴퓨터 회로 기계어 정리

메모리에서 기계어 받는 제어기

- 기계어를 보조 기억 장치로 부터 받을 수 있음

- 코드램 : 제어기 쪽에 연결된 SRAM

- 데이터램 : ALU쪽에 연결된 기존 SRAM

보조기억장치로부터 기계어를 받는경우/ 데이터를 받는 경우

- 기계어를 데이터램에 입력하지 않도록 해야함

-> 클록 펄스를 구분해서 입력

- 코드 램에 데이터 입력시 -> 데이터 램의 CLK에 펄스 X 코드램의 CLK 펄스 O

- 데이터 램에 데이터 입력시 -> 데이터 램의 CLK에 펄스 O 코드램의 CLK에 펄스 X

컴퓨터 회로 총 정리

데이터의 저장

- 메모리의 하위주소에서 상위주소로 저장

리틀 엔디언

- 하위 바이트 부터 저장

빅 엔디언

- 상위 바이트 부터 저장

컴퓨터가 처리하는 데이터

- 처리 데이터 = 동작 명령어, 계산 데이터

하버드 아키텍처

- 명령어(8비트) -> 코드 램에 저장, 데이터(8비트) -> 데이터 램에 저장

=> 분리된 메모리 저장하는 방식

폰 노이만 아키텍처

- 명령어(8)와 데이터(8)를 합쳐(16비트) 같은 메모리에 저장하는 방식

- 메모리는 16비트 데이터를 출력함

- 상위 8비트는 제어기, 하위 8비트는 ALU로 전달

하버드 아키텍처와 폰 노이만 아키텍처

- 하버드 아키텍처는 메모리가 분리되어 데이터 입출력과 명령어 처리 동시 수행 가능 -> 빠른 속도

<-> 메모리가 분리되고 별개의 어드레스 디코더 제어로 회로가 복잡 => 고비용

- 폰 노이만 아키텍처는 램을 하나로 줄였지만 동작방식은 하버드 아키텍처와 비슷

16비트 CPU

- 데이터를 16비트 씩 처리 -> 2바이트씩 SRAM 주소를 이동해야함

=> 프로그램 카운터를 2씩 늘려줌

8비트, 16비트, 32비트, 64비트 CPU 구분 기준

- 데이터 버스 폭과 ALU의 데이터 처리 크기

16비트 CPU 구조

OPCODE

- LDA = Load to A

- STA = Store from A

'컴퓨터과학 > 컴퓨터, OS' 카테고리의 다른 글

| NAND2Tetris 1 - 불 논리 (0) | 2020.04.25 |

|---|---|

| NAND2Tetris 0 - 소개 (0) | 2020.04.25 |

| ALU~보조기억장치 (0) | 2020.04.24 |

| 가산기~주기억장치 (0) | 2020.04.24 |

| 메모리~램 (0) | 2020.04.23 |