전자석으로 불끄는 회로

- 입력이 0이면 출력이 1

- 입력이 1이면 출력이 0

=> 인버터

인버터

- 입력과 출력을 반대로 해주는 회로

피드백 회로

- 인버터의 출력이 다시 입력으로 들어감

ex) 출력이 0 -> 입력 0 -> 출력 1 -> 입력 0 -> 출력 1

인버터-피드백 회로의 출력 그래프

- 0과 1의 규칙적인 반복

=> 클록 신호

오실레이터

- 특정 속도로 클록 신호를 발생시키는 장치

- 크리스털로 만듬

-> 온습도 등 외부 요인에 영향을 적게 받으면서 규칙적인 진동을 내기 때문

- 모든 디지털 장비에는 크리스털 오실레이터가 사용됨

* 디지털 회로에서 오실레이터는 사람의 심장과 같은 역활

* 모든 디지털 장치는 오실레이터의 클록 신호를 기반으로 동작

전자석 -> 릴레이 -> 인버터 -> (+피드백 연결) -> 오실레이터

릴레이와 트랜지스터

- 릴레이와 npn형 트랜지스터는 똑같이 동작

=> 트랜지스터는 릴레이의 반도체 버전

+ 트랜지스터로 논리 연산가능

AND 게이트

OR 게이트

NAND 게이트

전자석 -> 릴레이 -> 인버터 -> (+피드백 연결) -> 오실레이터

트랜지스터 -> 논리 게이트

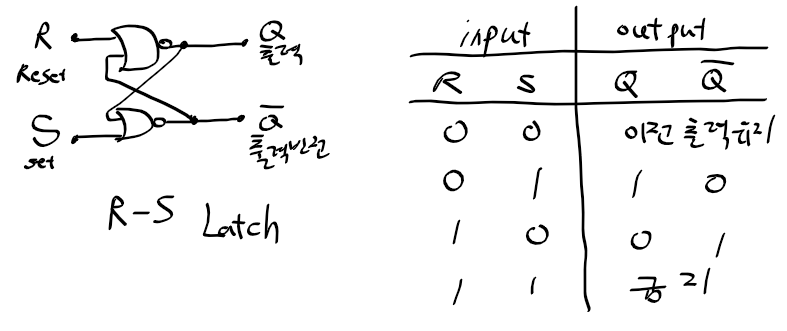

R-S 래치

- R(Reset), S(Set)

- Latch : 잠금

=> 논리게이트와 피드백 회로로 회로에 전류가 걸림 -> 데이터 저장

- R-S 래치는 1비트 값 저장하는 디지털 회로

R-S 플립 플롭

- R-S 래치는 출력으로 Q와 Q바의 값이 항상 반대여야 함

-> Q와 Q바가 동시에 0이 되는 입력 R, S가 (1,1) 되면 안됨

=> 2개의 AND 게이트 + CLK 신호 사용 => R-S 플립플롭

* R-S 래치를 간략히 추상화하여 표시

R-S 플립 플롭의 진리표

- 입력 R과 S를 전환 할 때 (1,1)이 될 위험이 큼

-> R-S 플립플롭에서 CLK가 0일때만 R-S 신호를 바꾸도록 하면 해결

J-K 플립플롭

- R-S 플립플롭에서 여전히 허용되지 않는 입력 값 상태가 존재

-> 3-입력 AND게이트 활용하여 해결 => J-K 플립플롭

J-K 플립플롭의 진리표와 타이밍 다이어그램

라이징 에지와 폴링 에지

- 오실레이터의 클록 출력은 0과 반복

- 라이징 에지 : 0에서 1로 바뀌는 순간

- 폴링 에지 : 1에서 0으로 바뀌는 순간

전자석 -> 릴레이 -> 인버터 -> (+피드백 연결) -> 오실레이터

트랜지스터 -> 논리 게이트 -> R-S 래치 -> R-S 플립플롭 -> J-K 플립플롭