1. CPU 개요

CPU

- Central Processing Unit

- 산술 연산과 논리 연산 처리

산술 연산

- +/- 연산

논리 연산

- AND/OR/NOT 등 연산

컴퓨터의 5대 장치

- CPU의 제어/연산 장치

- 나머지로 입력/기억/출력 장치

메모리(주기억장치)

- CPU에 연산할 데이터와 프로그램 전달

- CPU는 연산 결과를 메모리에 저장(혹은 레지스터에)

ALU

- Arthmetic Logit Unit 산술 논리 장치

디지털과 0,1

- 디지털을 표현하기 위해 0과 1로 나타냄

- CPU 내부 등 전기 신호로 LOW 전압, HIGH 전압 과같이 전기 신호로 이용

2. 디지털 연산

10진수와 2진수

- 2진수로 10진수 표현 가능

- 1011(2) -> 11(10)

- 4(10) -> 100(2)

고정 소수점

- 0.000001

- 12340000.

부동 소수점

- 1.23 x 10^2

- 1.23 x 10^-6

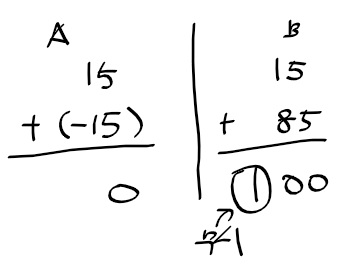

2진수 뺄샘과 보수

- 보수와 덧셈을 하면 뺀 것과 같음.

- "-15"는 "+(-15)"와 동일함

- "-15"를 다른 숫자로 표현하는 방법이 필요

- B 식의 자리 올림(캐리)를 제외하면 A식과 결과가 동일함

- 위의 경우 15에 대해 85는 100의 보수.

보수

- 더하면 자리수가 올라가는 수.

- 뺄셈 = "보수와 덧셈"

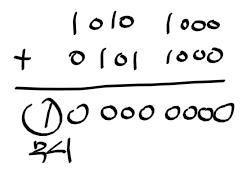

2진수 뺄셈과 2의 보수

- 캐리를 무시하고 결과 모든 자리가 0이 되는 보수를 2의 보수라 한다.

2의 보수 구하는 방법

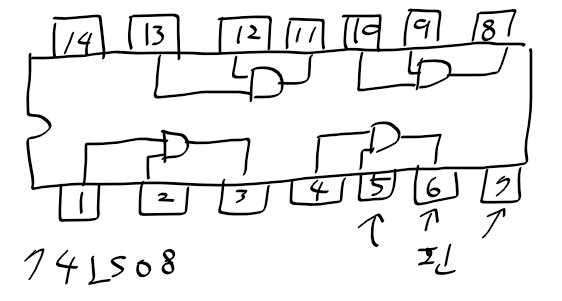

IC(Integrated Circuit 집적 회로)

- 논리 회로의 모음

- 아래는 예시로 74LS08

논리 회로(Logic Circuit)

- 입력 2개, 1개 출력

- 대표적으로 AND, OR, NOT

- 이 논리 회로/논리 게이트(Logic Gate)들을 조합하여 NAND, NOR, EXOR 등 만듬

드모르간의 정리

- AND연산과 OR 연산은 치환 가능

반 가산기(Half Adder)

- 덧셈 연산하는 회로

- 1비트(1자리) 끼리 덧셈 가능

- 여러 자리의 덧셈 처리 불가 -> 전가산기

전 가산기(Full Adder)

- 총 3개 입력 = 기본 입력 2개 + 캐리 여부(자리 올림) 입력 1개

- 출력 2개 = 합 S와 캐리 C

- 반 가산기 2개와 OR 게이트 1개로 구성

순차 자리 올림 가산기(Ripple Carry Adder)

- 가산기를 이어 여러 자리의 덧셈을 할수 있는 가산 회로

- 가산기 4개를 이으면 4 자릿수 연산 가능

래치(Latch)

- 데이터를 유지하는 것

- "1" 상태를 유지 -> 래치

플립 플롭(FF:Flip Flop)

- 값을 기억하는 회로

- 1비트 데이터(0/1)을 기억할 수 있음.

- 대표적인 플립플롭으로 RS 플리플롭, D 플립플롭, T 플립플롭

-> 메모리와 레지스터, 카운터 등도 플립플롭으로 만듬

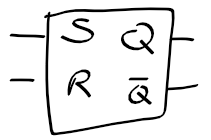

RS 플립플롭

- R(Reset), S(set)를 입력으로 받는 플립플롭

- S=1 이면 Q=1

- S=0 이면 Q=0

RS 플립플롭 - NAND 게이트

- RS 플립플롭은 NAND 게이트로 구현 가능

- S와 R에 둘다 1을 입력하여 Q와 Q부정이 1이 되선 안됨

D 플립플롭

- D(Data)를 의미, C는 Clock(클록)

- 라이징 에지 때 값을 기억하는 플립플롭

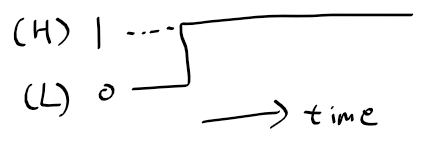

클록

- 일정 주기로 0과 1을 반복하는 디지털 신호

- 회로의 동작 상태를 맞추는데 필요

상승 에지와 하강 에지

- L->H로 변하는걸 상승 에지(Rising edge)

- H->L로 변하는걸 하강 에지(Falling edge)

D 플립플롭의 동작

T 플립플롭

- T(Toggle)

- 입력이 0->1 또는 1->0이 될때 출력이 바뀌는 플립플롭

카운터 회로

- 이 회로는 하강 에지로 T-FF을 연결하며, 카운트 업 하고 있음.

-Q2, Q1, Q0순으로 2진수를 보면 T 시간에 대한 수를 나타냄.

프로그래밍을 이용한 회로 설계

- 하드웨어 기술 언어(HDL = Hardware Description Language)를 이용하여 회로를 생성 가능

- 논리 회로 기호로 회로를 설계했지만 최근에는 간단한 경우 외에는 사용하지 않음

- 최근에는 FPGA(Field Programmable Gate Array)를 이용해서 개발 함.

-> 동일한 FPGA를 써도 전혀 다른 IC를 만들 수 있음.