증폭

- 증폭 : 신호를 키우는 것

- 처리 방식 : 아날로그, 디지털

- 방법 : 선형(이득이 일정), 비선형(입력 크기에 따라 이득이 변화)

BJT 증폭기 동작

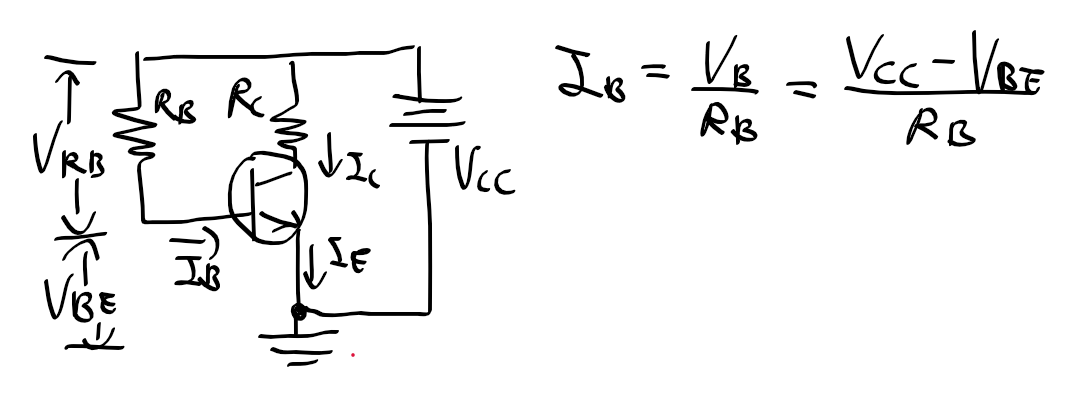

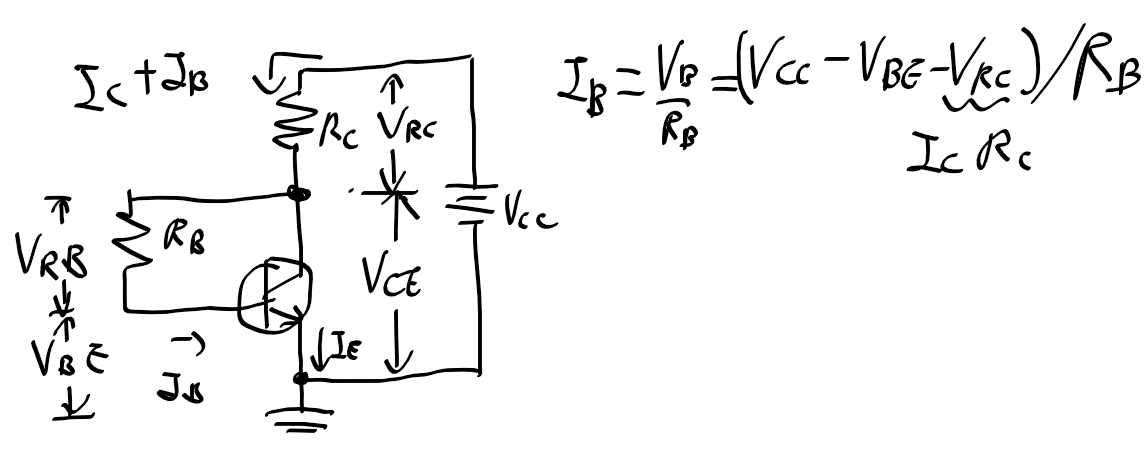

- 트랜지스터의 바이어스는 직류 동작 B C E

- 교류신호의 증폭은 교류 동작 b c E

- 증폭기에 인가되는 직류 전원과 교류 전원을 나누어서 해석해 보자

직류 교류 표기

- 직류는 대문자 첨자

- 교류는 소문자 첨자

- 순시치의 경우 소문자

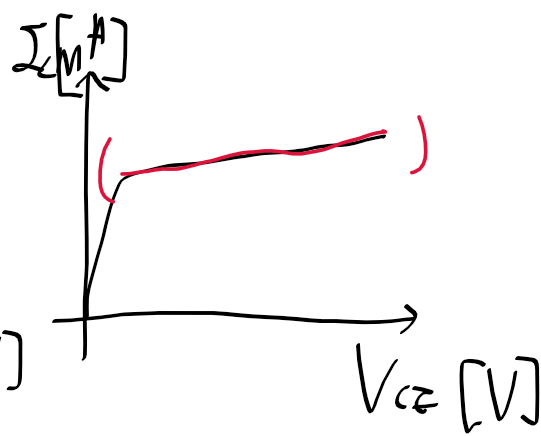

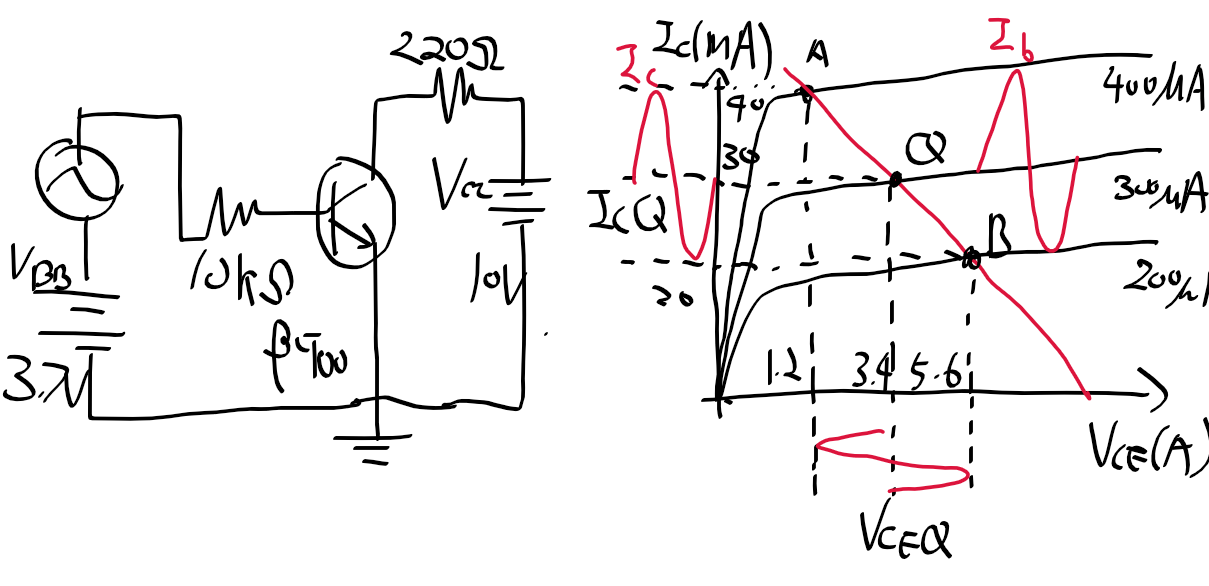

컬렉터 특성곡선 재정리

- I_B가 고정되도록 V_BB 설정, V_CC = 0

=> V_CE = 0V, V_BE = 0.7V

=> B-C 접합 : 순방향, B-E 접합 : 순방향 바이어스

- V_CC 증가 시(V_CE가 0.7V 이하)

-> I_C 증가(V_CE가 0.7V까지 급상승),

+ V_CE는 0.7V이상 증가하지 않는걸로 보자(V_BE = 0.7V인 이상 B-C가 순방향 바이어스이므로)

- V_CC 증가 시(V_CE 0.7V 초과)

-> B-C 접합 : 역방향, B-E 접합 : 순방향 바이어스

-> I_C는 거의 일정하게 유지

V_CE가 더 증가해도, I_B가 고정되었으므로 공핍층 증가

= 베이스 영역의 재결합에 필요한 정공 수 감소

= 적은 I_B로 I_C 증폭 가능 = Beta_DC가 조금 상승

=> 활성 영역에서 V_CE가 크게 오르는 동안 I_C는 조금씩 증가

* 컬렉터 특성 곡선 유의 사항

- 컬렉터 특성곡선은 고정된 I_B를 가정하여, V_CE 증가에 따른 I_C 변화를 나타냄

- 활성 영역에서 전류가 수백배 증폭하지 않고 수평에 가깝게 조금씩 증가하는건, I_B 고정, Beta가 조금씩 커지기때문

- I_C = Beta_DC * I_B이므로 I_B와 I_C의 값과 단위가 나와있거나 여러 I_B 값에 대한 곡선을 보는것이 이해하기 좋음

* 진짜 컬렉터 특성곡선이 이해가 안되서 며칠을 해맸다.

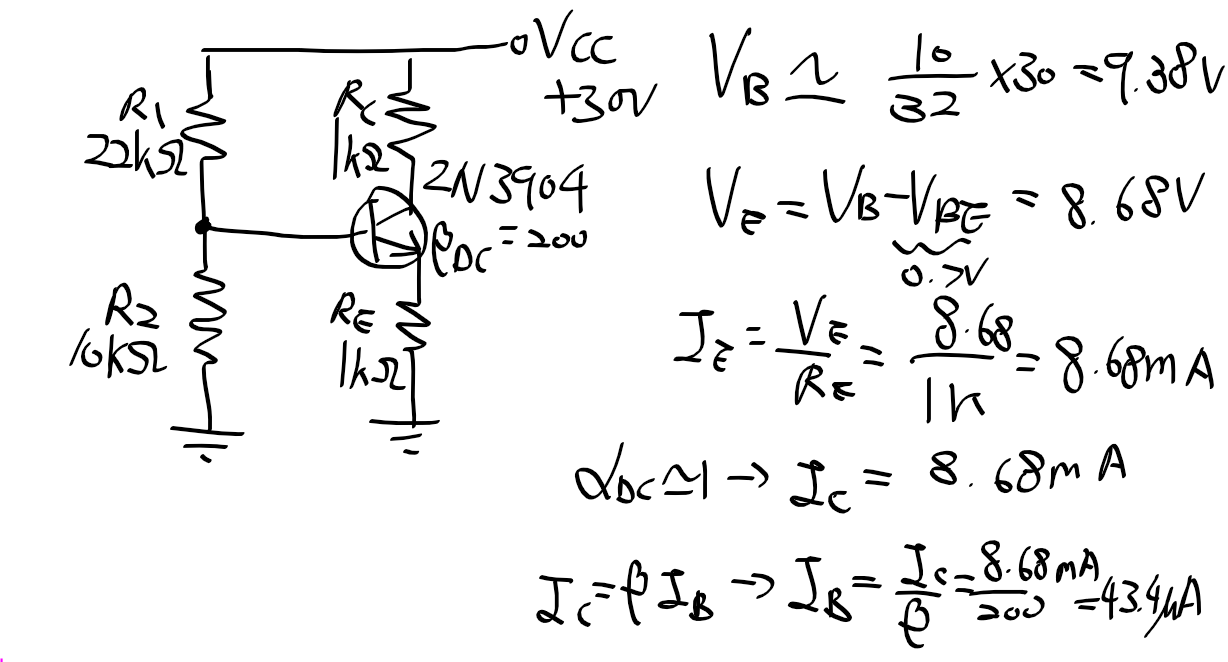

선형 증폭기

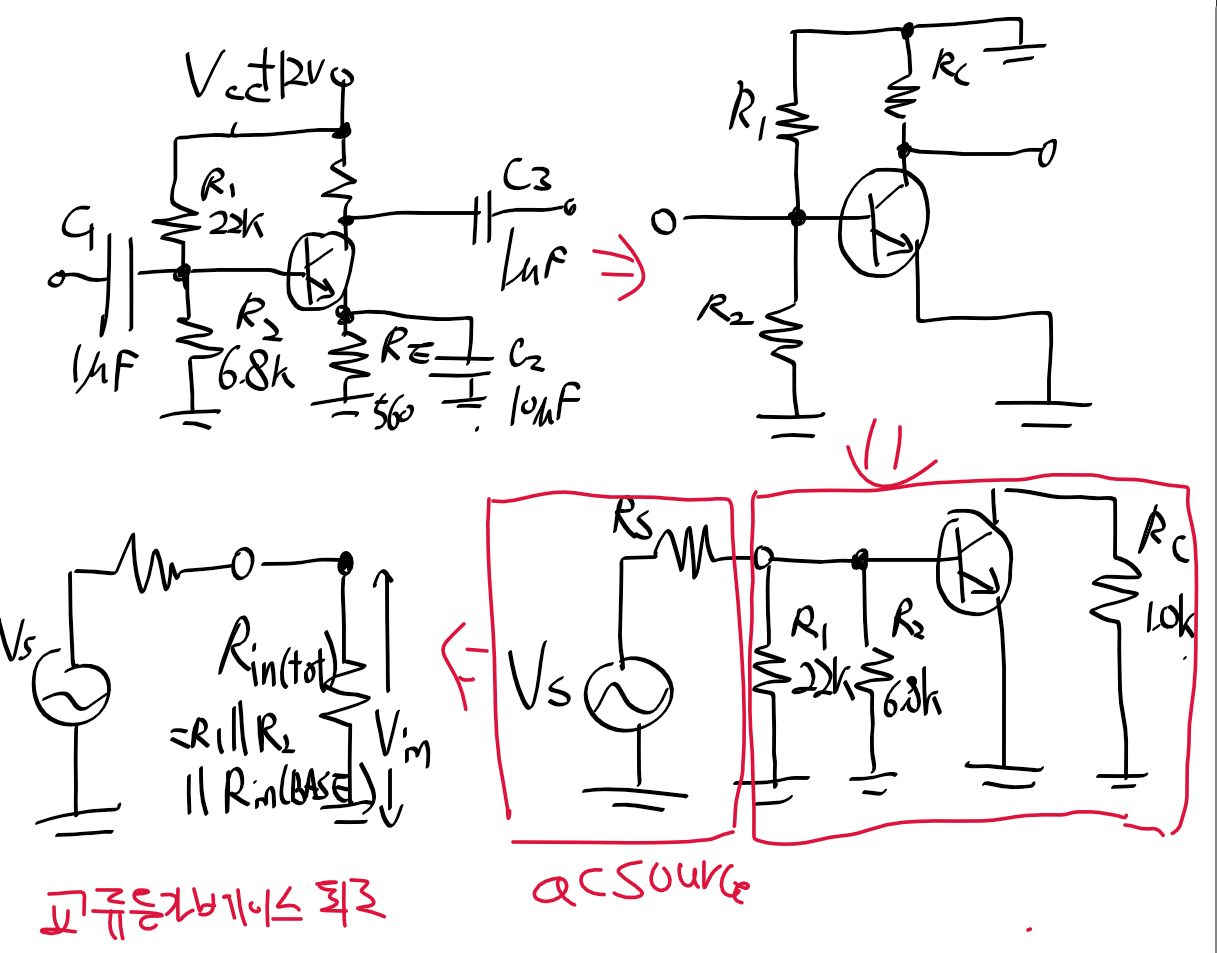

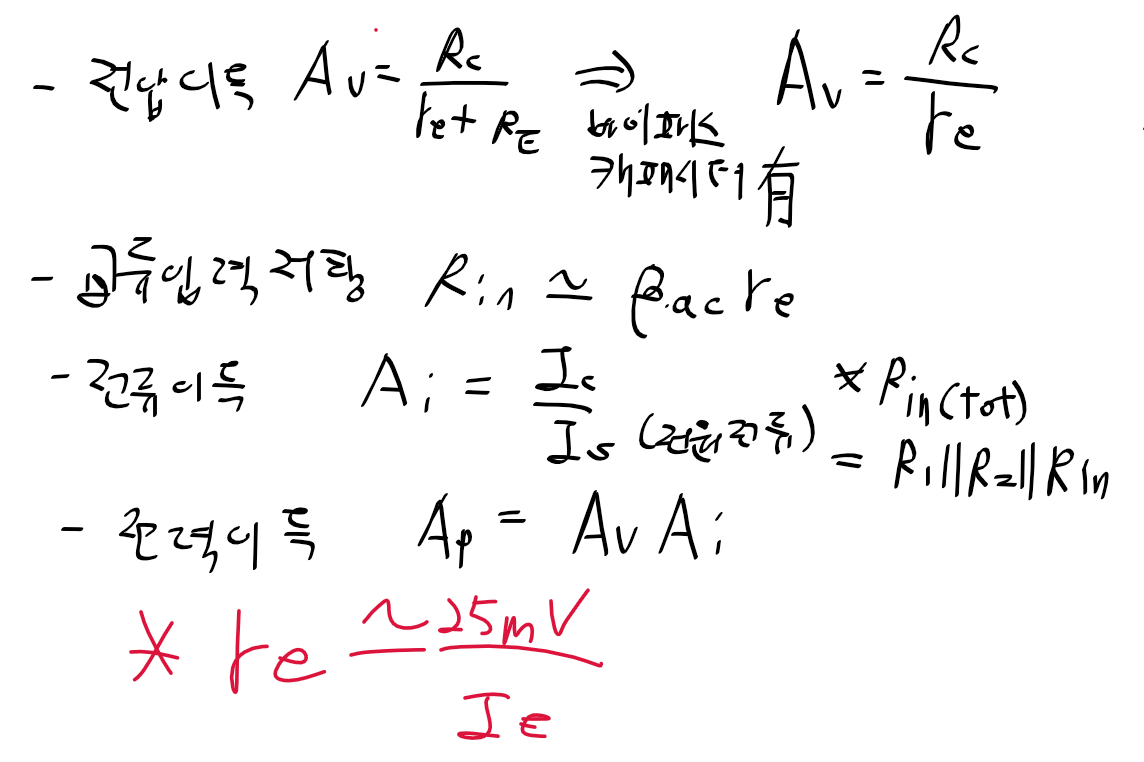

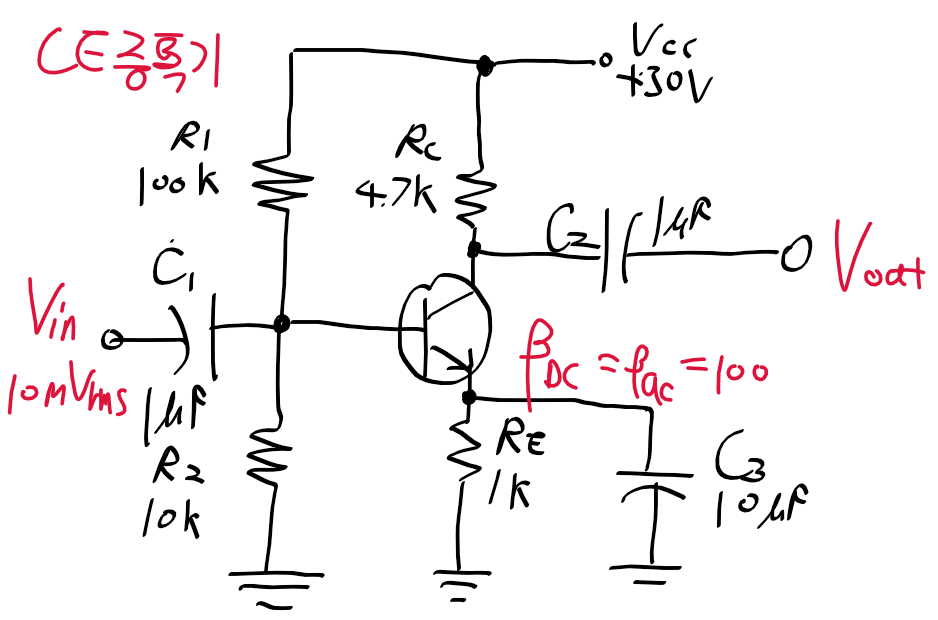

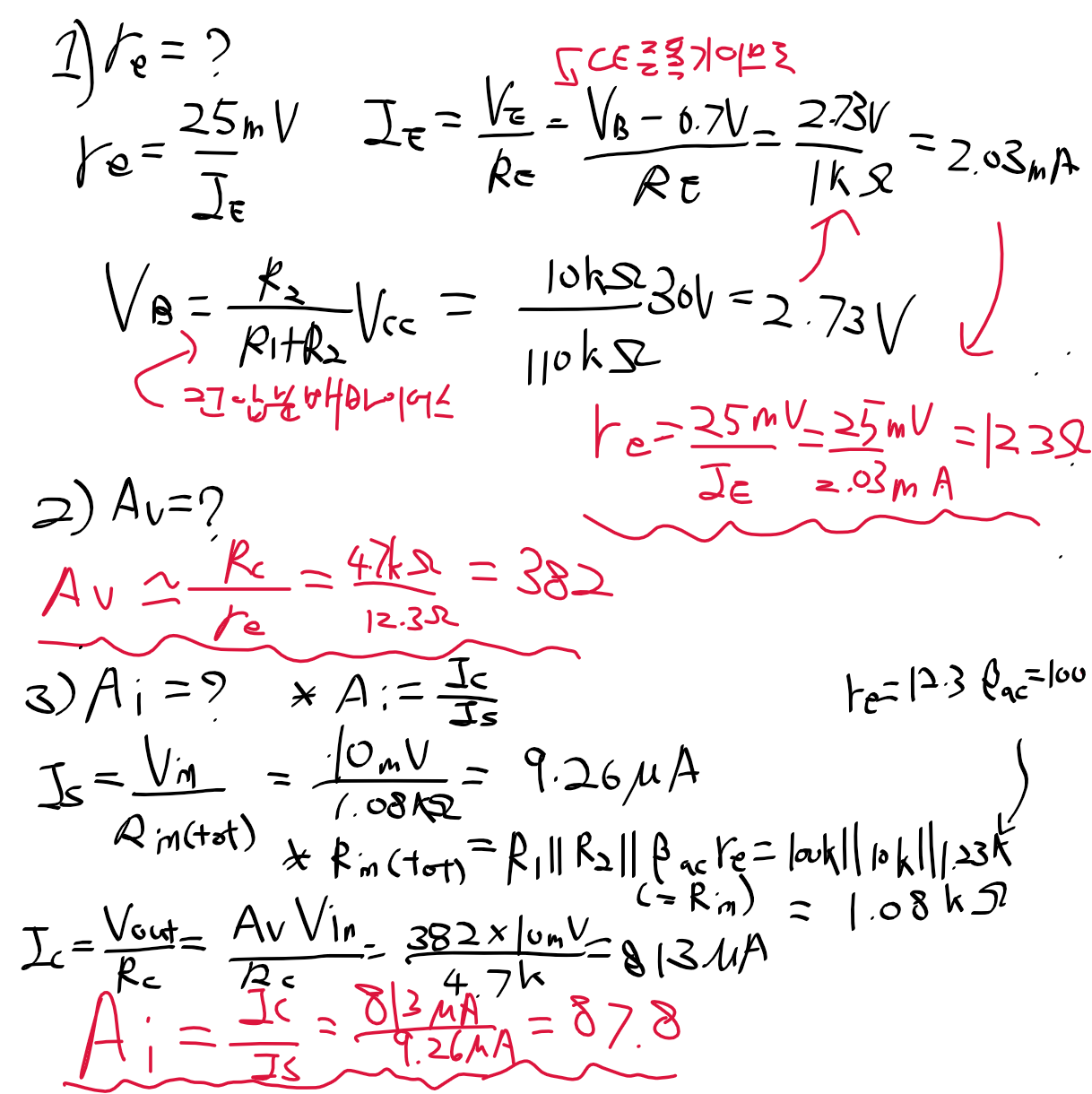

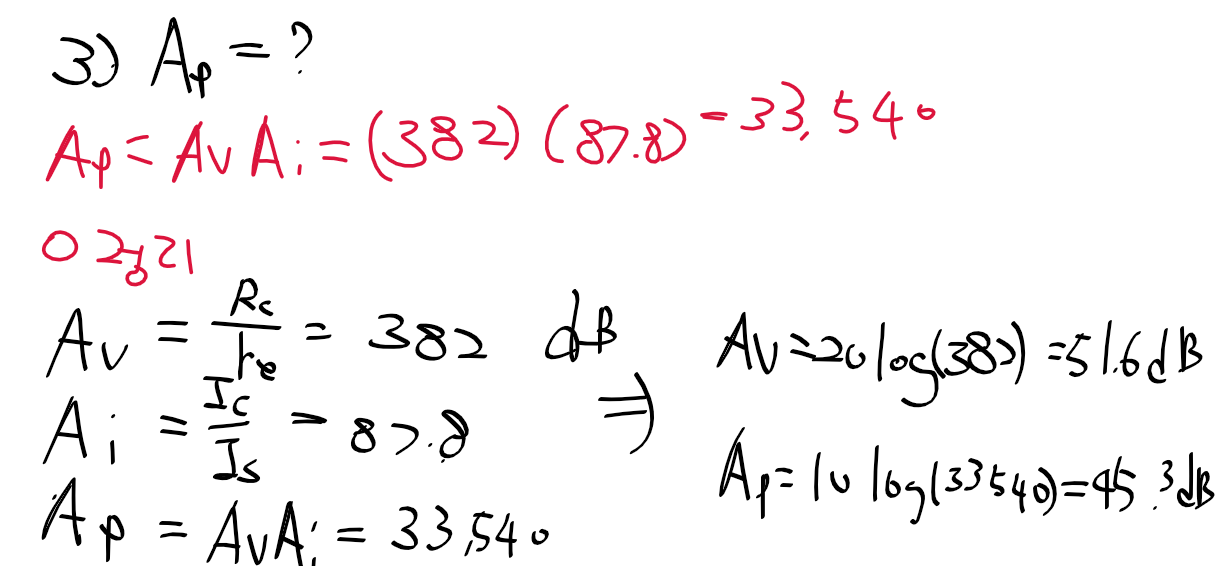

- 증폭 과정 : 내부 저항 R_s를 갖는 교류 전압원을 전압 분배 바이어스 소신호 증폭기로 증폭

- V_ce : R_C에 의한 전압 강하로 출력 전압은 컬렉터 전류의 위상과 180도 반전

직류 부하선 그래프 해석

- 직류 바이어스로 적절한 부하점 Q를 설정하면 교류 신호는 Q점을 기준으로 변동

- I_c는 I_b의 크기에 비례

- V_ce는 교류 전류 I_c의 크기에 반비례

- 해석 순서

1. I_b 변화에 따라 I_c가 바뀜

2. I_c 변하면서 V_ce가 바뀜

=> I_b -> I_c -> V_ce 순서로 보자

교류 등가회로

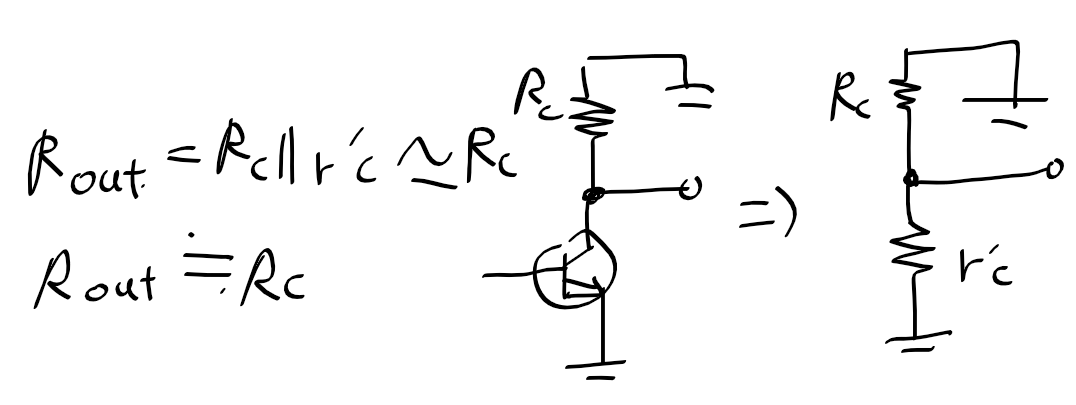

- 트랜지스터의 동작을 나타내기 위해 트랜지스터의 내부 파라미터 이용

- r, h 파라미터가 있다.

r 파라미터

- 증폭기를 이해하기 위해 등가 회로로 표현

- 저항성 r 파라미터는 BJT에서 보편적으로 사용

- 트랜지스터 각 단자의 저항을 의미함.

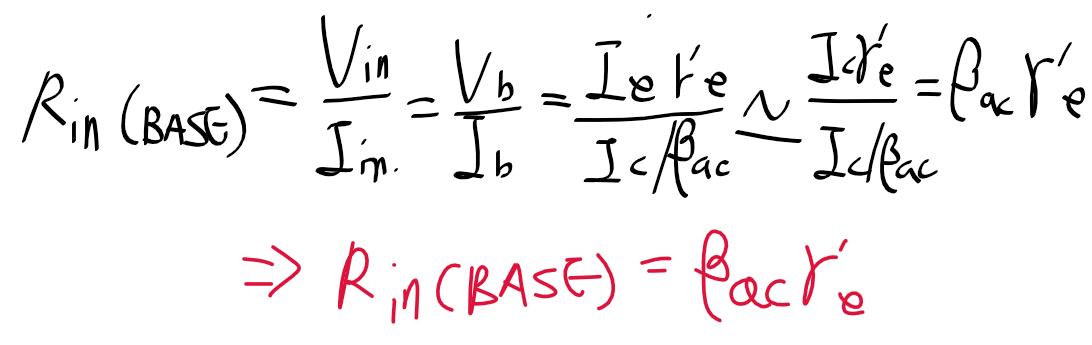

- r'b는 매우 작으므로 단락상태로, r'c는 매우 크므로 개방 상태로 보고 r'e만 남는 등가회로로 해석 가능

r'e

- r'e는 25mV/I_E로 구함

직류 베타 beta_DC와 교류 베타 beta_ac

- I_C와 I_B 특성 곡선은 비선형

=> 교류 전류 이득 beta_DC != 직류 전류 이득 beta_ac

h 파라미터

- h(hybrid) 파라미터는 입력 전류/전압과 출력 전류/전압의 관계로 정의

- 입출력 전류/전압을 측정하여 트랜지스터 특성 파악 가능

- 각 h 파라미터들을 입력/출력단 개방하여 쉽게 측정

트랜지스터 증폭기

- 입출력 단자 조합에 따라 공통 이미터/베이스/컬렉터 증폭기로 구분

증폭기 분석

- h 파라미터로 다음의 r 파라미터를 구하여 분석 가능