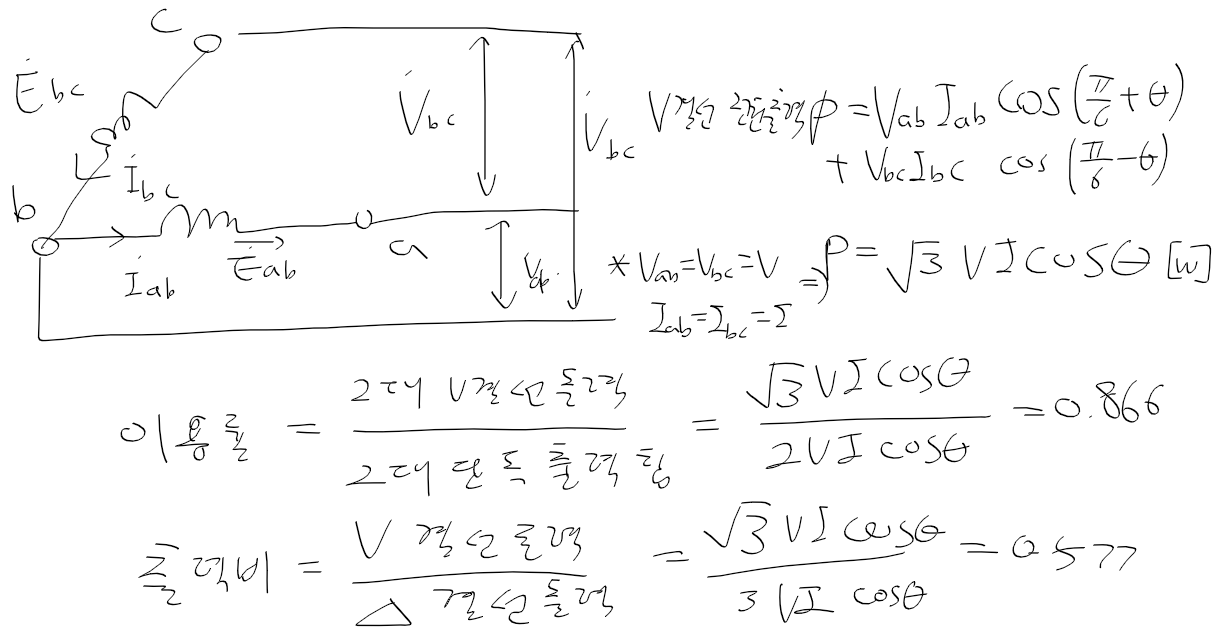

2전력 계법

- 불평형 3상 3선 회로를 2개의 전력계로 구한 전력의 합/차로 3상 전력을 측정하는 방법

- 3상 유효 전력 P = P1+P2

- 3상 무효 전력 Q = root(3)(P1 - P2)

- tan theta는 Q/P로 구할 수 있다.

재정리

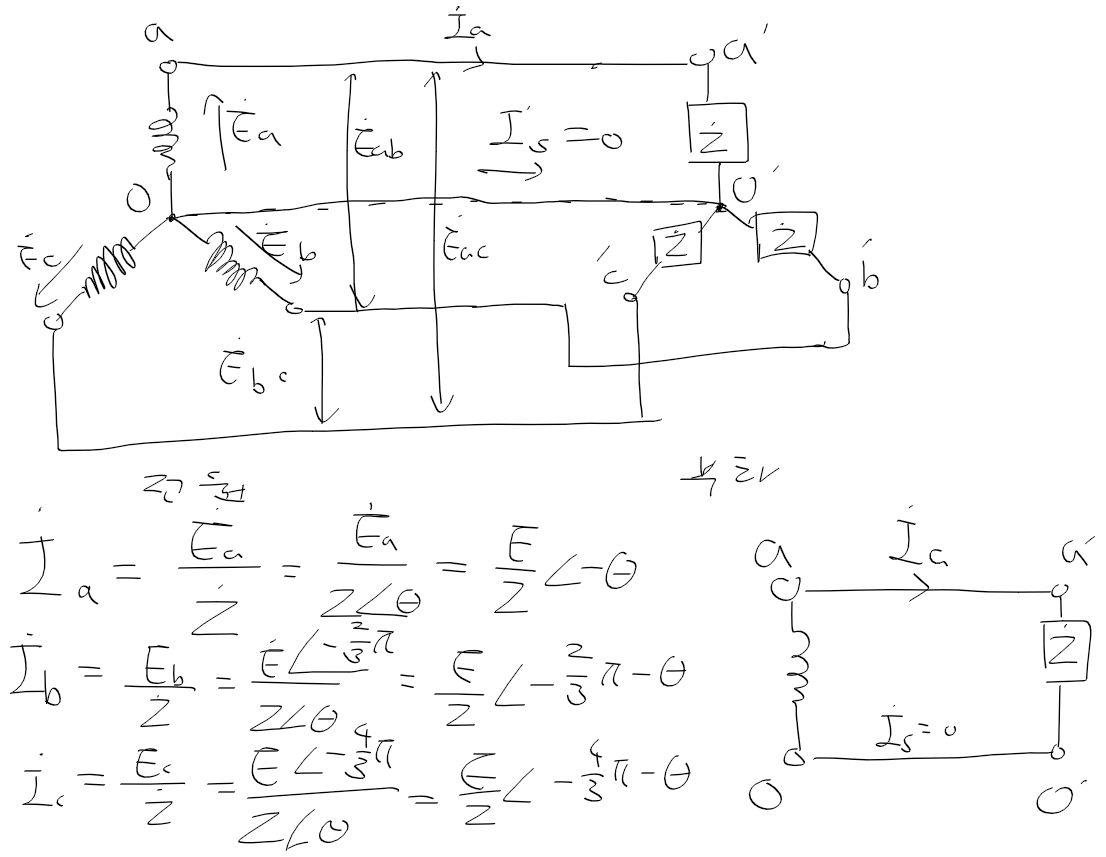

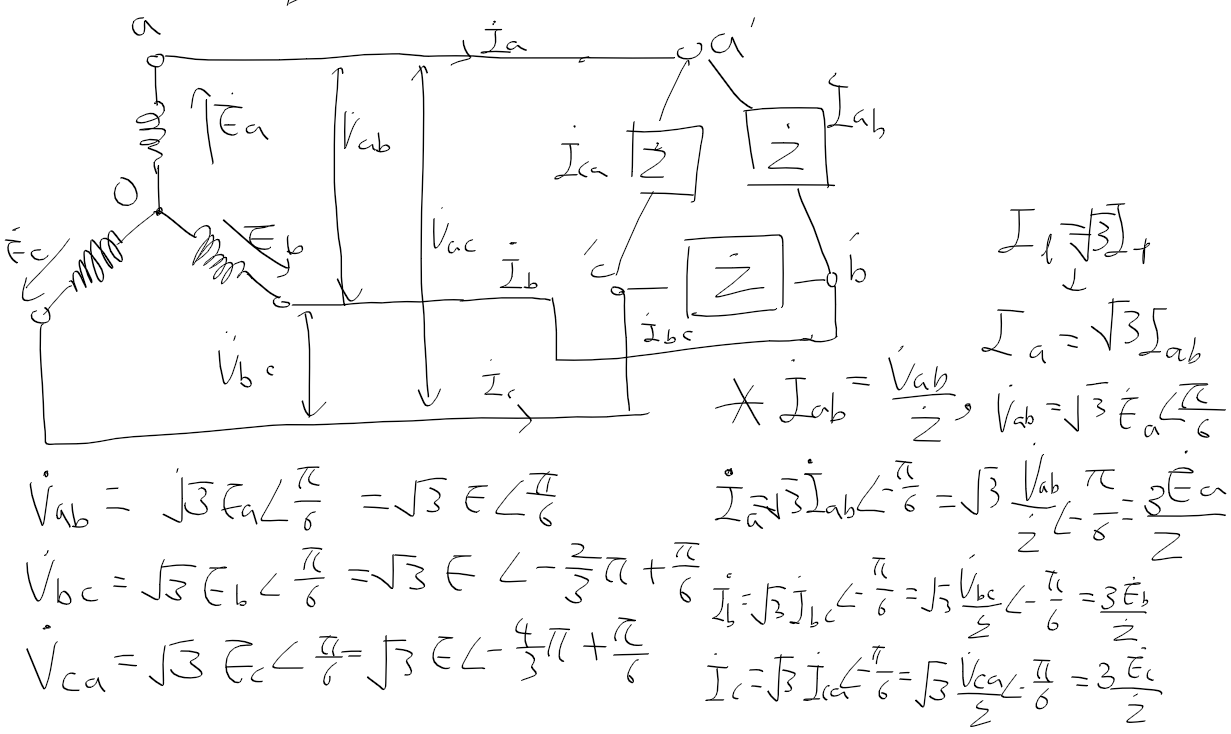

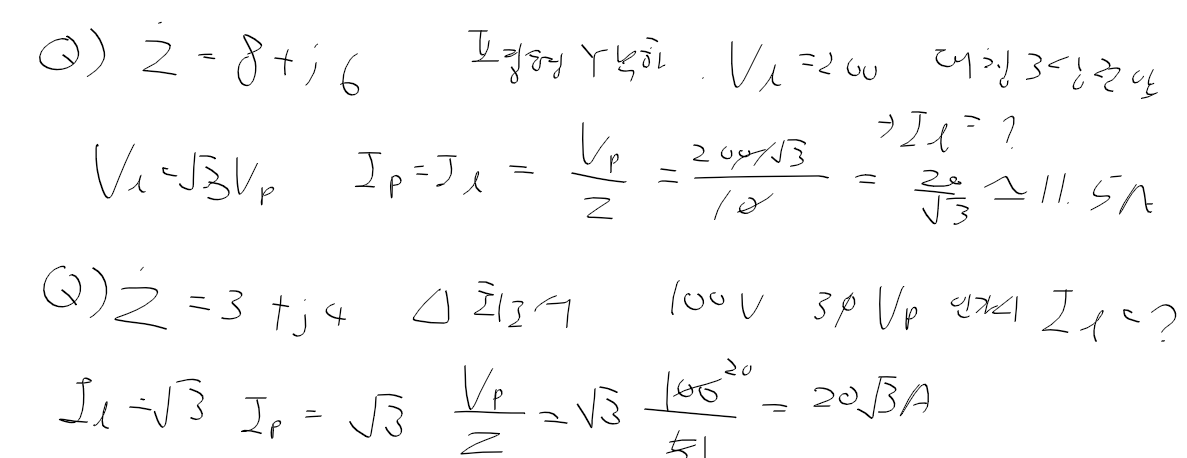

- 대칭 3상회로 : 기전력=, 위상각 2pi/3

- 대칭 3상 전원 회로 : 대칭 3상 회로 + 내부임피던스=

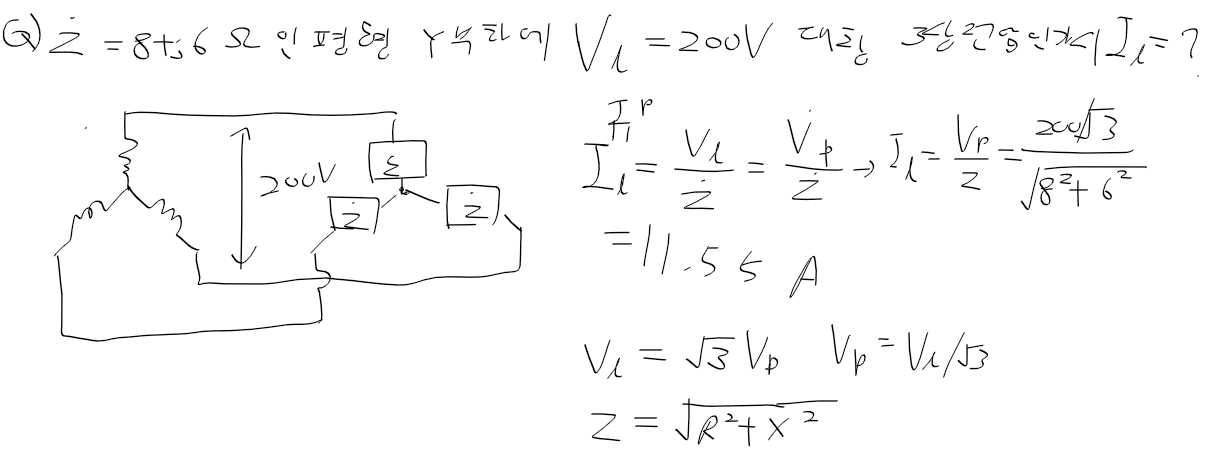

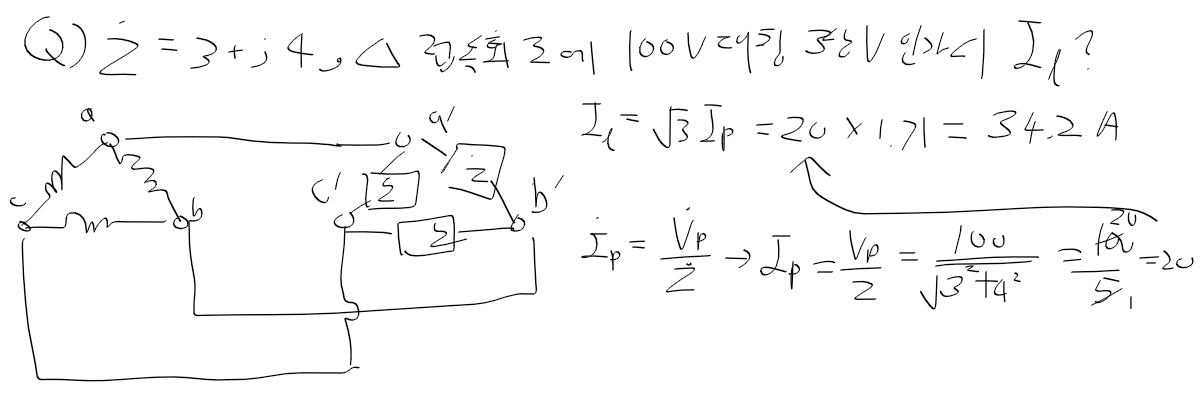

- 평형 3상 부하 회로 : 3상 부하 임피던스 =

- 평형 3상 회로 : 대칭 3상 전원 회로 + 평형 3상 부하 회로

=> 불평형 회로 = 3상 부하 임피던스가 같지 않은경우?

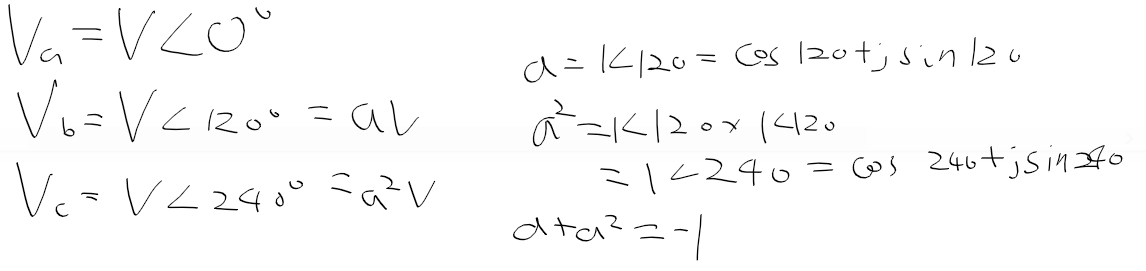

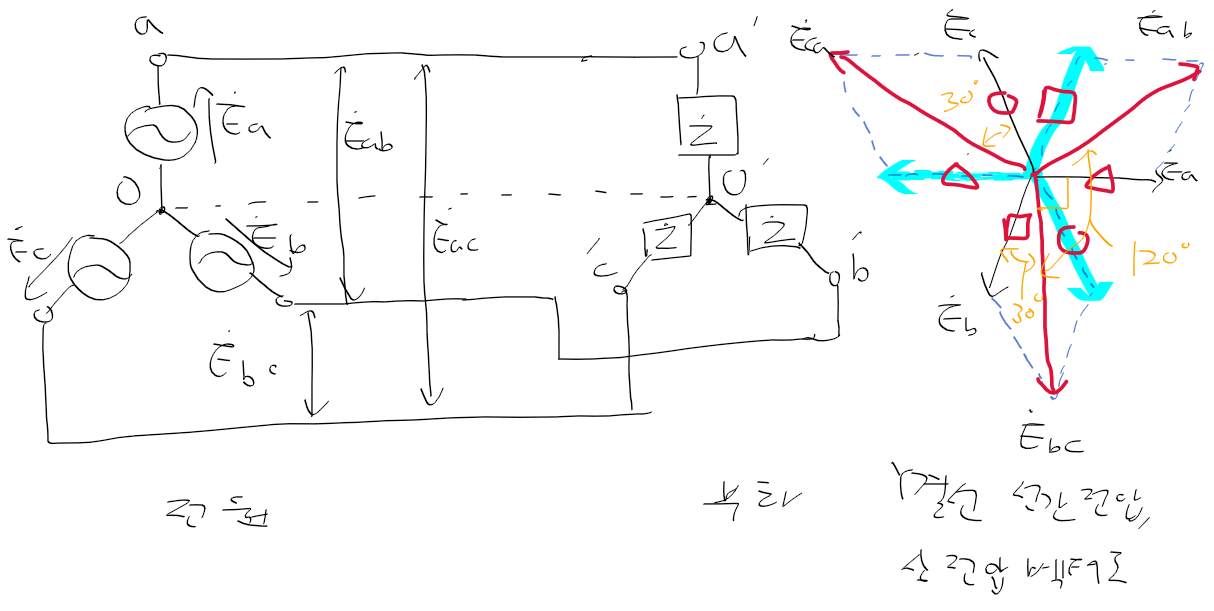

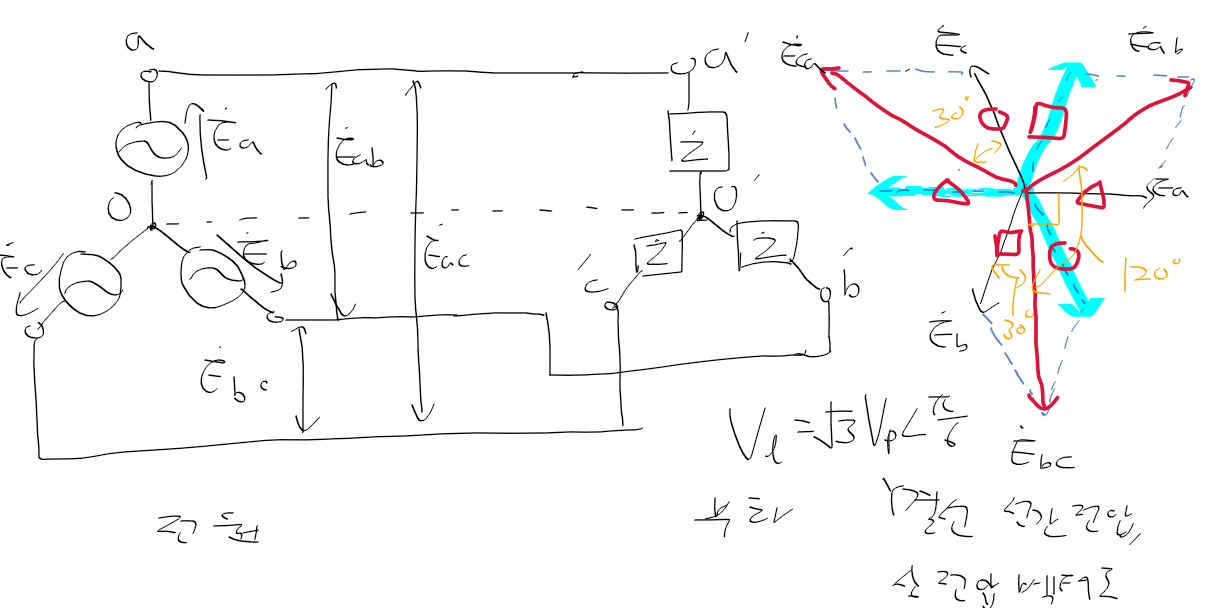

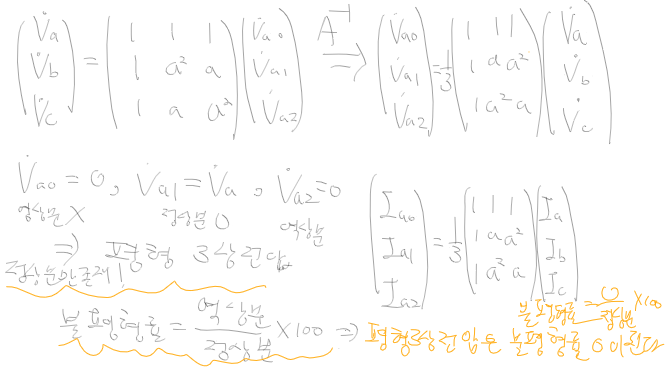

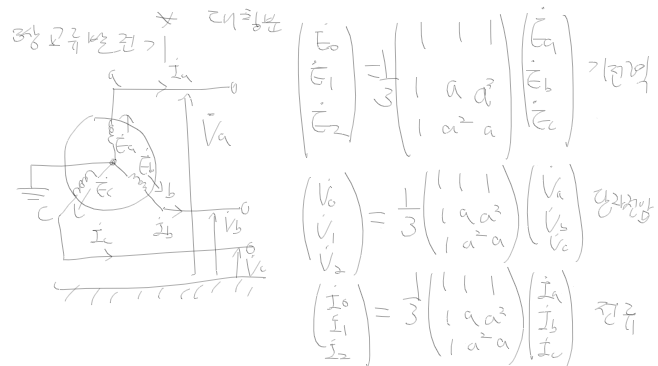

대칭 좌표법

- 평형 회로 문제를 쉽게 계산하기 위한 방법

- 상순이 a,b,c인 평형 3상전압 V_a1, V_b1, V_c1

+ 상 순이 반대인 평형 3상전입 V_a2, V_b2, V_c2

+ 방향과 크기가 같은 3상 전압 V_a0, V_b0, V_c0

= 불평형 전압 V_a, V_b, V_c를 얻는다.

=> 반대로 불평형 전압을 영상분/ 정상분/역상분으로 분해 가능하다.

- 영상분 : 방향과 크기가 같은 전압성분

- 정상분 : 상순이 a, b, c인 전압성분

- 역상분 : 상순이 반대인 전압성분

- 벡터 연산자를 이용하여 불평형 3상 전압 벡터를 정리하면..

- 전류도 동일한 관계를 가진다.

- 대칭분 = 영상분 + 정상분 + 역상분

- 정상분만 존재하는 경우를 평형 3상 전압

- 역상분이 존재하지 않은경우 => 불평형률 = 0 => 평형 3상 전압

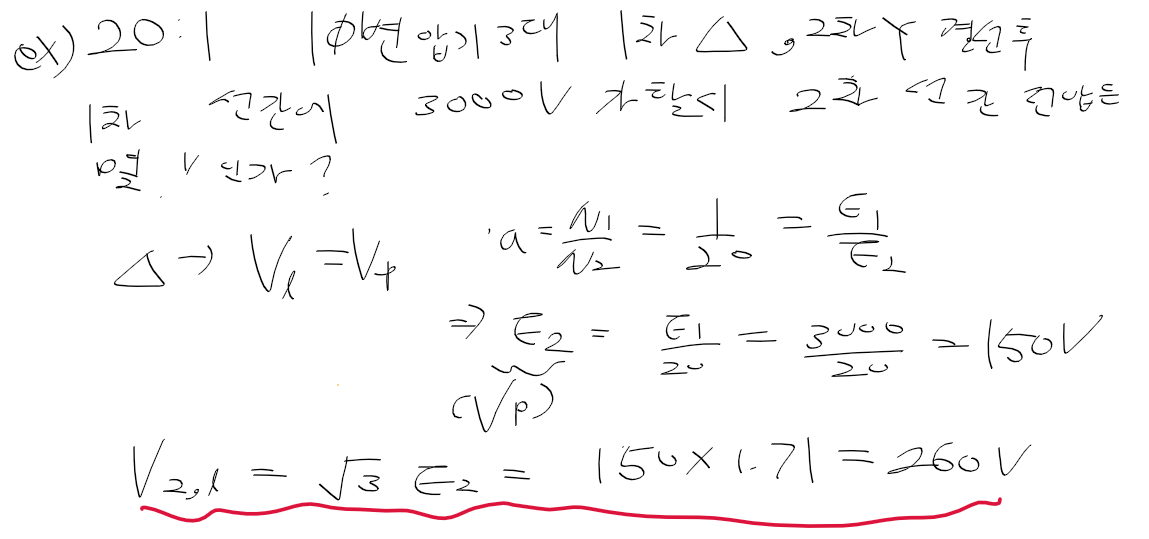

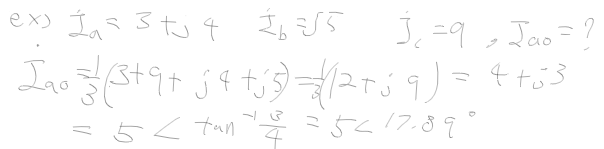

예제

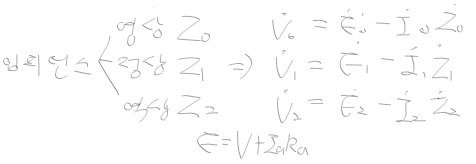

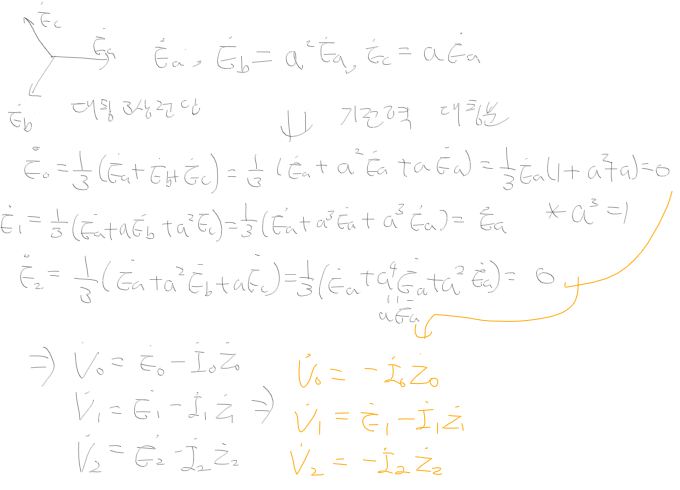

대칭 3상 교류 발전기

- 대칭분 행렬을 통해 기전력, 단자전압, 전류를 다음과 같이 정리 할 수 있다.

- 영상분, 정상분, 역상분에 대한 임피던스가 주어지면 각각의 단자 전압은 다음과 같다.

- 위 3상 교류발전기가 대칭 3상 발전기이므로 a상으로 각상 기전력을 바꾼 후 단자전압을 다음과 같이 정리할 수 있다.

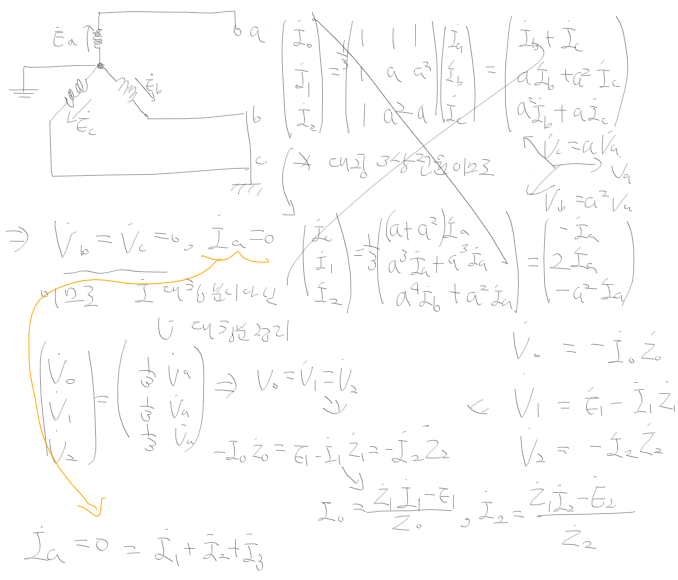

3. 3상 회로 고장 계산

1) 1상 지락

- a상 지락 시, b와 c상에 흐르던 전류들이 사라지고 i_b = i_c = 0, 접지된 a쪽으로 흐르므로 접지전류 i_a를 구해야한다.

* a로 전류가 흐르나, 부하가 존재하지 않으므로 V_a =0이 된다.

2) 2상 지락

- b, c상 지락

=> a상으로 흐르는 전류가 없어진다 i_a = 0.

=> 부하가 없으므로 단자전압 v_b = v_c =0이 된다.

'기타 > 신호, 회로, 제어' 카테고리의 다른 글

| 복) 전자회로 1 - 다이오드 (0) | 2022.04.08 |

|---|---|

| 회로이론 - 8. 비정현파 교류 (0) | 2022.04.07 |

| 회로이론 - 7-2. 3상 교류 회로 2 (0) | 2022.04.07 |

| 회로이론 - 7-1. 3상 교류 회로 1 (0) | 2022.04.07 |

| 전자 회로 11 - 제너 다이오드 (0) | 2022.04.04 |