회로와 집적회로

- 개별 소자 회로 : 소자들을 모아 구성한 회로

- 집적 회로 : 많은 소자들을 집적하여 만든 회로

집적회로에서의 연산증폭기

- 여러 소자들을 모아 이상적인 증폭기에 만든 것

- 편리, 소형, 신뢰, 저가로 아날로그 시스템에서 널리 사용

- 기본적으로 차동 증폭기를 사용.

증폭기의 종류

- 전류 증폭기 : 입력 전류 i_I에 의해 출력단 종속 전류 A_i * i_i이 조절되는 증폭기

+ 이상적인 전류 증폭기 : 전류 이득 A_i = inf, 입력 저항 R_i = 0, 출력 저항 R_o = inf(부하로 많이간다)

- 전압 증폭기 : 입력 전압 v_i에 의해 출력단 종속 전압 A_v * v_i가 조절되는 증폭기

+ 이상적인 전압 증폭기 : 전압 이득 A_v = inf, 입력 저항 R_i = inf, 출력 저항 R_o=0(부하에 많이 걸린다)

- 전달 컨덕턴스 증폭기

- 전달 저항 증폭기

연산 증폭기

- 두 입력과 하나의 출력으로 구성 + +V_CC(Source), -V_EE(sink)의 이중전원사용

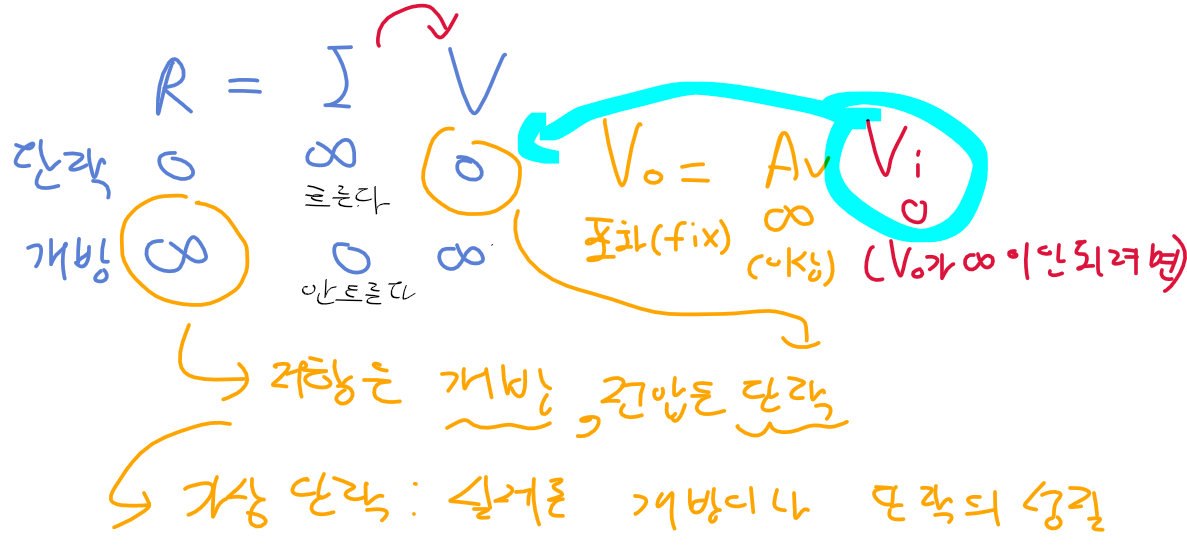

- 비례 상수 A_o는 개루프(open loop) 이득을 의미

=>v+는 위상반전없이 증폭, v-는 위상반전되어 증폭

- 출력은 공급 전원인 -V_EE <= v_o <= +V_CC 범위로 제한되며, 초과시 해당 범위로 포화)

- 이상적인 연산증폭기에 가깝게 만들기 위해 수십개의 트랜지스터 사용 + 개루프 이득이 아주 큼

연산증폭기와 등가회로

- 이상적인 연산 증폭기에 가깝게 입력 저항은 무한대, 출력 저항은 0, 이득은 아주 크게 만들어 진다.

- A_o가 100k라 할때, 1V 출력을 얻으려면 v_i는 10uV면 된다

- 포화 전압이 +-5V인 경우, v_가 +-50uV를 넘어가면 포화된다.

=> 비교기로 사용하려면 포화시키면 된다.

+ uV 단위는 매우 작으므로 0으로 보자.

- 증폭기로 사용하기 위해서는 선형영역이 넓어지는것이 좋다.

연산증폭기의 동작

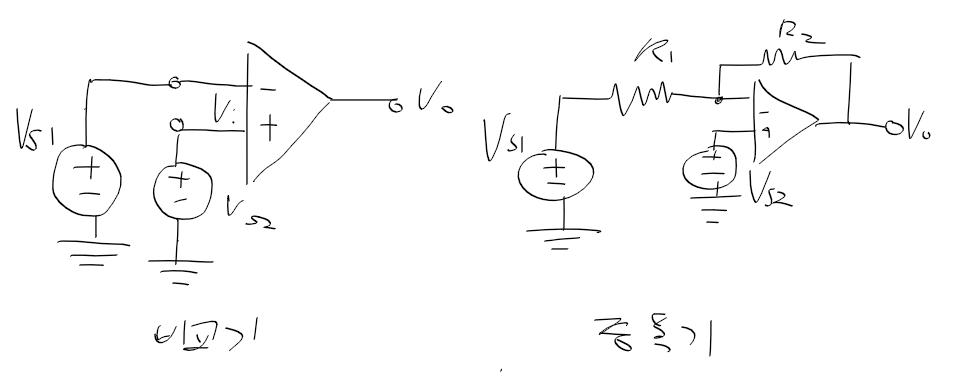

- 비교기 : V_in이 +V_cc, -V_EE로 포화시 비교기로서 비선형적인 동작

- 증폭기 : V_o의 일부가 반전 입력으로 궤환. 궤환 비율은 분배 저항 R1, R2로 결정

-> 출력이 반전 입력단으로 들어가므로 기존의 출력 v_o와 위상이 반대로

-> -가 되어 출력에 반영되어 개루프때보다 이득이 줄어든다.

=> 부궤환을 통해 선형영역을 늘린다 => 증폭을 조절하기 좋아진다 => 증폭기로 사용한다.

가상 단락

1. 연산증폭기의 입력 저항 R_i는 무한대이므로 두 입력 사이에는 (i+) + (i-) = 0전류가 흐르지 않아 개방 회로가 된다.

2. 연산 증폭기의 전압 증폭률 A_v = 무한대에 가까워야하나 v_o가 포화되지 않으려면 v_i는 0에 가까워야한다.

=> v_i = 0이 된다는것은 단락 상태를 의미한다

*개방시는 V가 무한대가 됬었고, 단락시에는 0이므로

- 가상 단락 : 개방과 단락의 성질을 동시에 가지는 것 => 연산 증폭기 해석에 유용

반전 증폭기

- 비반전 입력은 접지, 반전 입력에만 입력을 주는 증폭기

1. 비반전 입력 : 접지처리되어 입력단 전압 v_+ = 0

2. 단락 성질 : 반전 입력단의 전압 v_-는 비반전 입력단의 전압 v_+과 같으나 비반전 입력 전압이 0이다.

=> Vs와 v_- 사이 전위차가 존재하므로 저항 R1에 전류가 흐른다. => i = Vs/R1

3. 개방 성질 : 입력 저항이 무한대 = > 개방 상태 => 반전 입력단자에 가지 않고, R2로 간다.

=> 출력단 전압 v_o는 저항 R2에서 전압 강하된 전압을 뺀 정도가 된다.

=> v_o = (v_-) - (R2 * i) = -R2 * i

- 정리하면 폐루프 이득 A_v를 구할 수 있으며, 이득 A_v는 R1과 R2를 조절하여 바꾼다.

* 입출력 전압의 위상은 폐루프 이득이 음수이므로 반대가 된다.

비반전 증폭기

- 비반전 증폭기는 +에 입력을 - 단자에 접지를 하는 증폭기로 앞서 본 가상 단락의 개념으로 증폭도, 출력을계산하자

비반전 증폭기의 궤환 전압과 궤환 전압 이득, 전체 저항

- 두 저항을 이용한 전압 분배를 떠올리자. 궤환 전압 v_f와 전압 궤환 이득 beta를 구할 수 있다.

- 전체 입력 저항 R_if는 V_in = (V_+) - (V_-)로 부터 구할 수 있다.

'기타 > 신호, 회로, 제어' 카테고리의 다른 글

| 전자산기 정리 - 전자회로 (0) | 2022.04.12 |

|---|---|

| 복) 전자회로 4 - 연산 증폭기 응용 (0) | 2022.04.09 |

| 복) 전자회로 2 - BJT (0) | 2022.04.08 |

| 복) 전자회로 1 - 다이오드 (0) | 2022.04.08 |

| 회로이론 - 8. 비정현파 교류 (0) | 2022.04.07 |