ATmega 128

- 마이크로 컨트롤러

* 마이크로 컨트롤러 = CPU Core (Architecture) + CPU Peripheral(Controllers)

-> 마이크로 프로세서 단독으로 있는게 아니라 주변장치 포함

주변장치 예시 : 타이머/카운터, TWI(I2C), ADC, USART, SPI, 메모리, 발진회로 등

마이크로 컨트롤러로 할수 있는 일?

- 대부분의 제어 가능

-> 모든 제품들은 마이크로 컨트롤러 내장

ex) 드론, 로봇, 냉장고, 세탁기, 차량 등

ATmega 128 의 특징

- 데이터 시트로 확인 가능

1. 뛰어난 성능 (Advanced RISC Architecture)

- Most single clock cycle execution -> 대부분의 명령들을 한 클럭만에 실행 가능

- 32 * 8 bit 범용 레지스터 : 8비트 범용 레지스터 32개 내장 -> 고속 접근 가능한 범용 목적 8비트 메모리가 32개

2. 많은 메모리(Program 메모리, Data 메모리)

- 128 KB Flash (프로그램=명령어 메모리)

- 4 KB SRAM, 4KB EEPROM (데이터 메모리)

3. 다양한 주변장치 지원

- Timer/Counter 4개(8비트 카운터 2개, 16비트 카운터 2개), TWI(I2C) 2포트, 10bit ADC

- USART(비동기 통신) 2채널, SPI(주변장치용 직렬 통신 인터페이스), On-chip Oscillator(=8MHz, 발진기)

* 프로그램 다운로더 ISP 장비는 SPI 프로토콜로 플래시 메모리에 프로그램을 write 한다.

- ATmega128 : 0~16 MHz / 4.5 ~ 5.5V

- ATmega128L : 0~8 MHz / 2.7 ~ 5.5V(저전력에서 동작)

ATmega128 내부 구조

- ATmega128의 핀 구조, 내부 버스에 연결된 컨트롤러를 보여주는 회로도

ATmega 128 코어 부분

- 32개의 8비트 범용 레지스터가 연산장치 ALU와 연결

- 데이터 메모리 SRAM과 EEPROM가 데이터 버스와 연결

- 좌측에 프로그램 메모리 플레시 메모리가 존재

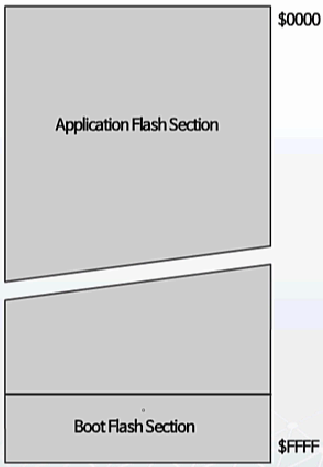

프로그램 메모리 플래시 메모리의 메모리 맵

- 부트 플래시 섹션과 어플리케이션 플래시 세션으로 나뉨

- 부트 플래시 세션 : 부트 로더

- 어플리케이션 플래시 세션 : 프로그램 저장

- 16비트로 명령어들이 저장

데이터 메모리맵

- 32개 범용 레지스터, 64개 IO 레지스터은 동일

- ATmega 128은 IO 레지스터 160개 확장 가능

- 내부 SRAM 8비트 크기의 4096개

폰노이만 구조

- CPU와 메모리 사이에 물리적으로 하나의 버스만 존재

- Von Neumann Bottleneck 발생

- 프로세서 <-주소/데이터 버스 -> 코드

하버드 구조

- 명령어와 데이터 버스가 분리되어 동시에 패치 가능

- 코드(명령어) <-주소/데이터-> 프로세서 <- 주소/데이터 -> 데이터

프로세서 구조

RISC(Reduced Instruction Set Computer)

- 하드웨어 구조가 단순함 -> 저전력 -> 모바일 장치에 적합

- 모든 명령어 길이가 동일 -> 코드 사이즈가 커짐

- Load Store Architecture로 많은 레지스터가 필요

- ATmega64, ATmega128, ARM, MIPS

CISC(Complex Instruction Set Computer)

- 복잡한 하드웨어 구조

- 명령어 마다 길이가 다름 -> 코드 사이즈가 작음

- RISC에 비해 작은 레지스터가 필요

- intel 8056, x86

일반적인 마이크로 컨트롤러 구조

- 고성능 마이크로 컨트롤러 = RISC + 하버드 구조 + 레지스터 중심

- 레지스터 중심 구조

1. 처리 속도 향상

2. 코드 사이즈가 작음

3. C언어 개발에 유리

CISC와 RISC 연산의 예

- 연산 예시 : A = B + C + D;

- CISC Type : 하나의 명령어로 여러번 ALU 연산

ADD R16, Mem[B], Mem[C];

ADD Mem[A], Mem[D], R16

- RISC Type : 하나의 명령에서에서 하나의 ALU 연산만 가능

LDI R17, Mem[B]

LDI R18, Mem[C}

LDI R19, Mem[D]

ADD R16, R17

ADD R16, R18

ADD R16, R19

파이프라인 동작

- RISC의 경우 하드웨어 구현이 간단하며 명령어 길이들이 동일함

- 파이프라인 사용하지 않을 시 동작 -> 작업 1개가 끝나야 다음 작업 수행(다른 작업들은 대기)

- 파이프라인 사용 시 -> 명령어 대기 시간 없이 다른 작업들을 동시에 수행

ATmega128 명령 처리 과정

- ATmega128은 2단계 파이프라인 구조로 설계됨

- 1주기 안에 명령어 1개 수행

ATmega 128 핀구조

- ATmega128은 전체 64개의 핀

- 프로그래밍 가능한 입출력 포트는 53개

PA, PB, PC, PD, PE, PF, PG까지 53개

입출력 포트 제어 관련 IO 레지스터

- 각 핀 1개에 입출력 레지스터 3개가 배당 -> DDR, PORT, PIN 레지스터

Data Direct Register DDRx Register

- 해당 핀의 입력/출력 모드 설정

- 해당 핀의 특정 비트가 0이면 입력 설정, 1이면 출력 설정

ex) PA의 0번 비트를 출력 설정시 -> *DDRA=0x00000001;

ex) PA의 0~3번 비트를 출력 설정시 -> *DDRA=0x00001111;

PORTx Register

- 해당 핀에 high를 출력할지 low를 출력할지 설정

- 0일시 0V output, 1의경우 5V output

PINx Register

- 핀으로부터 데이터 입력을 받는 레지스터

입출력 핀 구조

- DDR이 1로 설정 시 PORT의 값이 핀으로 출력

- DDR이 0으로 설정시 핀으로부터 입력을 PIN 레지스터에 저장됨

'로봇 > 전기전자&메카' 카테고리의 다른 글

| vmlab 다운로드 (0) | 2020.05.12 |

|---|---|

| 마이크로프로세서 메카트로닉스 제어 - 2 개발 환경 구축 (0) | 2020.05.12 |

| 전자 회로 (0) | 2020.04.22 |

| 전기수학3 (0) | 2020.04.21 |

| 전기 수학2 (0) | 2020.04.21 |