실행할 프로그램 + 데이터 -> 메모리에 저장

- 프로그램 접근 방법 이해 -> 실행 과정 이해

- 메모리 사용 -> HW측면 : 제어방식 고려, SW 측면 : 접근방식고려

- 한번에 읽을수있는 데이터 최소길이와 최대 길이 -> 데이터 구조를 정하거나 구조체 변수 선언시 필요

ARM 프로세서의 예외처리 절차

- 운영체제 개발, 초기화 프로그램 개발, 새 입출력장치 추가시 필요

- 임베디드 시스템에 새 디바이스 추가시 디바이스 드라이버가 제공되며 예외 처리 절차에 대한 상세한 이해 필요

(1) 메모리 구성

1) 메모리 저장 방식

2) 메모리 접근 방식

3) 메모리 맵

1) 메모리 저장방식

메모리 저장 방식

- 바이트 단위로 접근하는 메모리에 멀티 워드 데이터 저장

- 빅엔디언 방식 : MSB 부터 하위 어드레스에 저장

- 리틀 엔디언 방식 존재 : LSB 부터 하위 어드레스에 저장

ARM 프로세서의 메모리 저장방식

- 빅엔디언, 리틀엔디언 모두 지원

- ARM 프로세서 엔디언 선택 -> 외부 설정 핀, 시스템 설정 레지스터 사용

- ARM 11 코어의 경우 -> 2개의 외부핀, 15부 프로세서 c1 레지스터의 U,A,E 비트값으로 설정

- 컴파일 시 엔디언 적용 : -EB 빅엔디언, -EL 리틀엔디언

2) 메모리 접근 방식

- Word, Half-word, byte 단위 접근 가능

- 정렬된 메모리 접근 -> 워드 단위 접근 : 4배수 어드레스, 하프 워드 단위 접근 : 2의 배수접근

- 정렬되지 않은 메모리 접근 -> 하프/하프워드 단위 접근 모두 연속된 어드레스 사용.

3) 메모리 맵

- CPU가 메모리 접근시 사용하는 어드레스 공간 할당 방법

- 메모리 유형, 어드레스 범위, 접근제어 방식에 따라 메모리 공간 분리 사용

- 어드레스 공간 할당 방법 -> 가변 메모리맵/ 고정메모리맵(대부분 ARM프로세서 사용)

가변 메모리맵

- 메모리맵을 사용자가 결정

- 메모리가 단일한 어드레스 공간으로 구성

- 메모리 맵이 변경되면 어드레스 디코더 및 제어회로필요

고정 메모리맵

- 메모리맵을 프로세서가 결정

- 메모리 유형과 어드레스 범위가 사전에 결정

- 외부 추가회로 없이 프로세서로부터 제어신호 출력

(2) 예외 처리

1) 예외

2) 예외처리 절차

3) ARM에서의 예외 처리

4) 시스템 리셋

1) 예외

-프로세서 내부/외부에서 발생하는 작업 요청 또는 이상

- 내부 : 소프트웨어 인터럽트, 트랩

- 외부 : 인터럽트 포함

- 예외 발생시 현재 작업 중단 하여 신속히 처리

예외 처리기(exception handler)

- 예외 발생시 처리해야할 작업들을 정의

- 발생 시 실행죽인 작업을 중단하고 예외처리기 실행후 원상태로 복귀

- 예외 유형에 따라 우선순위 부여하여 예외처리

예외 처리 응답시간지연 exception latency

- 예외 발생시점서 처리기 진입할때까지 소요시간

- 시스템 실시간성 보장에 영향

예외 벡터 exception vector

- 예외처리기가 저장된 메모리 어드레스

예외 벡터 테이블 exception vector table

- 예외 벡터들을 모아놓은 테이블

- 프로그램 메모리 시작 어드레스부터 일정 크기 공간을 확보하여 저장

- 예외처리기로 분기하는 명령어들이 저장

예외 우선순위 priority

- 여러 예외가 동시발생시 처리 순서 결정

2) 예외처리 절차

1. 프로그램 실행중 외부에서 인터럽트 요청을 받거나 트랩이 발생

2. 현재 실행 위치를 stack에 저장.

3. 프로그램 시작위치를 예외 벡터로 변경

4-5 예외벡터에 저장된 명령어 jmp를 실행

6. 예외 처리기를 실행

7. 스택에 저장된 프로그램 시작위치를 복구하여 이전 작업을 다시수행

3) ARM에서의 예외처리

예외 처리기 진입 절차

1. 리턴 어드레스를 링크 레지스터에 저장

2. CPSR을 SPSR로 복사

3. CPSR 동작모드 비트 설정

4. 예외 벡터를 PC로 복사

- Thumb state에서 예외발생 시 -> Arm state로 자동변경, 인터럽트 disable 처리

예외 처리기로부터 복귀

- LR로부터 PC값 복사

- CPSR을 SPSR로 복구

- 예외처리 진입시 인터럽트 disable 시킨경우 disable 비트를 clear

예외 처리기 진입시 LR값과 리턴시 실행명령어

- ARM 프로세서 명령어 : 32/16비트 명령어 -> 예외발생시 현재 프로그램 카운터 + 오프셋값이 저장

- 예외 처리기 실행 완료 후 리턴시 오프셋 값 재조정 필요

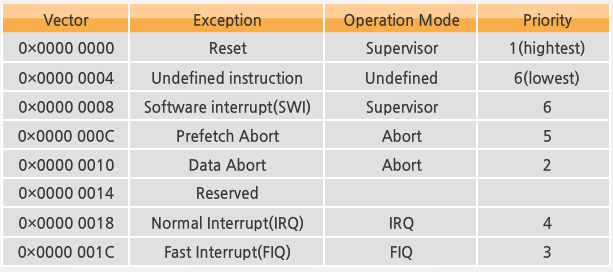

ARM 예외 벡터 테이블

- 테이블 엔트리 허용공간 : 32비트 -> 예외 처리기로 분기하는 분기명령 저장

- FIQ의 경우 벡터 테이블 가장 상위에 위치 -> 분기 명령없이 직접 예외처리기 저장가능

- 우선순위 : 리셋 예외 > 소프트웨어 인터럽트 <-> undefined 예외

ARM 예외 벡터 테이블

- 예외 발생 -> 실행 프로그램 중단 -> 예외 처리 프로그램 실행 -> 예외 처리

- vector : 실제 프로그램 메모리 어드레스값

- Exception : ARM 프로세서에서 사용하는 예외

- Operation Mode : 예외 발생시 동작 모드

- Priority : 예외 사이의 우선순위

- FIQ는 예외벡터 테이블 맨 마지막에 위치 점프 명령어로 분기할 필요없이 빠른 인터럽트 처리가능

4) 시스템 리셋

리셋 절차

1. nRESET Low: 실행중인 명령어를 버리고 새 명령어 fetch

2. nRESET High : R14_svc, SPSR_svcd의 현재 PC값과 CPSR 값 복사

3. CPSR의 동작 모드를 슈퍼바이즈 모드(M[4:0]= 10011)로 변경 + I/F비트 set -> 추가 인터럽트 방지

4. PC를 0x0000 0000 번지로 설정하여 리셋 예외처리기 실행

리셋 예외처리기

1. 시스템 초기화(시스템 클록 설정, 메모리 컨트롤러 초기화, 입출력 포트 설정)

2. 스택 초기화

3. 응용 프로그램 실행 : 운영체제 사용시 커널 호출, C프로그램의 main 함수 호출

'컴퓨터과학 > 임베디드' 카테고리의 다른 글

| ARM을 활용한 임베디드 시스템 설계 13 - shell 프로그래밍 (0) | 2020.05.04 |

|---|---|

| ARM을 활용한 임베디드 시스템 설계 7 - ARM 명령어 구조 (0) | 2020.05.04 |

| ARM을 활용한 임베디드 시스템 설계 5 - 메모리 (0) | 2020.05.03 |

| ARM을 활용한 임베디드 시스템 설계 4 - ARM 프로세서 구조 (0) | 2020.05.03 |

| ARM을 활용한 임베디드 시스템 설계 3 - 개발 (0) | 2020.05.03 |