마이크로 프로세서 이해

- 효율적 시스템 설계 필요

- HW 측면 : 플랫폼(메인보드) 설계

- SW 측면 : 프로그램 코딩 기법 이해 - 디버깅 작업에서 필수적임

(1) ARM 프로세서 개요

1) ARM 프로세서

2) ARM 코어 구조

3) ARM7TDMI

4) ARM 코어 로드맵

5) ARM 프로세서 요약

1) ARM 프로세서

- 영국 ARM사에서 개발한 32비트 RISC 프로세서

- 1983 영국 Acorn Computer 사에서 최초 개발

- Cortex-A, R, M 시리즈로 제공

ARM 프로세서 특징

- 32비트 임베디드 프로세서 시장 70%이상 차지

- 저전력 고성능으로 휴대용 장치에 주로 사용

- 16비트 명령어 제공

- Java 코드 가속

- DSP 기능

- 특정 메모리 영역제안 - 보안 기능

ARM 코어

- ARM 프로세서의 명령어 셋을 실행할수있는 하드웨어

- ARM 구조 -> ARM 코어의하드웨어구조

- ARM 시스템 코어 = ARM 코어 + 메모리 유닛(버퍼, 캐쉬,MPU 등)

ARM 코어 제공 형태

- 하드 매크로 셀 Hard macro cell : 레이아웃 수준 설계, 설계 변경 불가, 코어 크기 및 전원정압 고정

- 합성가능한 코어 Synthesizeable core : HDL 사용하여 RTL 수준으로 제공, 코어크기-내부메모리 변경가능, 기능변경불가

HDL (Hardware Description Language)

- 논리 회로를 텍스트로 표현하는 언어

- VHDL, Verilog HDL이 표준으로 채택

RTL (Register Transfer Level)

- 디지털 시스템을 레지스터 사이 데이터 전송 관계로 표현하는 방식

2) ARM 코어 구조

ARM 코어 특징

-32 비트 RISC CPU 코어

- RISC 타입의 기본 구조인 로드-스토어 구조

- 빠른 인터럽트가 가능하도록 설계

- 데이터 저장방식은 빅엔디언과 리틀엔디언 선택가능

32비트 RISC

- 데이터 기본 처리단위 : 32비트

- 명령어 셋 구조 : RISC

- 간단하고 적은 명령어 -> 간단한 코어구조 & 빠른 명령어 실행 속도

Load-Store 구조

- 모든 데이터 처리는 레지스터를 대상으로 함

- 메모리 인터페이스는 load /store 명령어만 사용

- 메모리상 데이터 Load 명령어로 레지스터에 로딩 후 연산

- Store 명령어로 메모리에 저장

빠른 인터럽트 처리

- 빠른 인터럽트 모드 제공

- 동작 모드별 중요 레지스터 뱅킹 -> 사전에 중요 레지스터 여러 셋준비

메모리 저장 방식

- 아래 둘중하나 선택하여 메모리 사용 유연성을 높임

- 빅 엔디언 : 최상위 비트가 하위 어드레스에 먼저 저장 -> 모토로라 IBM, 대부분 RISC 프로세서

- 리틀 엔디언 : LSB가 하위 어드레스에 먼저 저장 -> 인텔 계열 프로세서

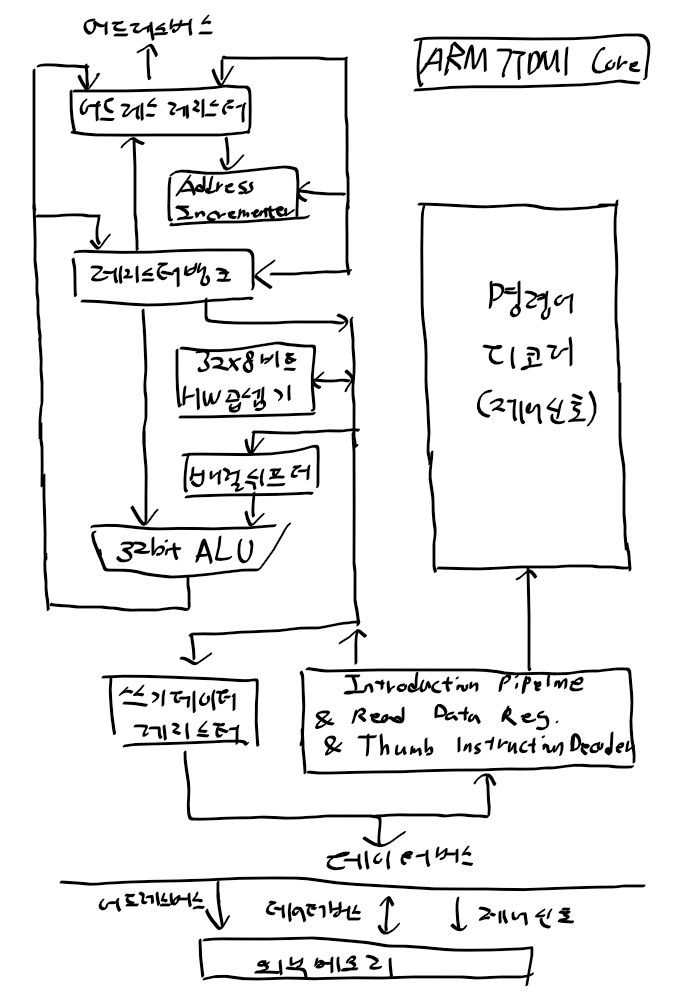

3) ARM7TDMI Core

- ARM 코어를 가장 잘 설명할수 있는 간단한 구조

- 32비트 ALU, 레지스터 뱅크, 어드레스 레지스터, 쓰기데이터 레지스터, 명령어 디코더 등으로 구성

- 폰 노이만 구조를 따름 - 프로그램 메모리와 데이터메모리가 같은 경로를 사용

- 중간에 배럴 쉬프터가 한 명령어로 ALU 연산과 쉬프트 동작 동시에 수행 가능

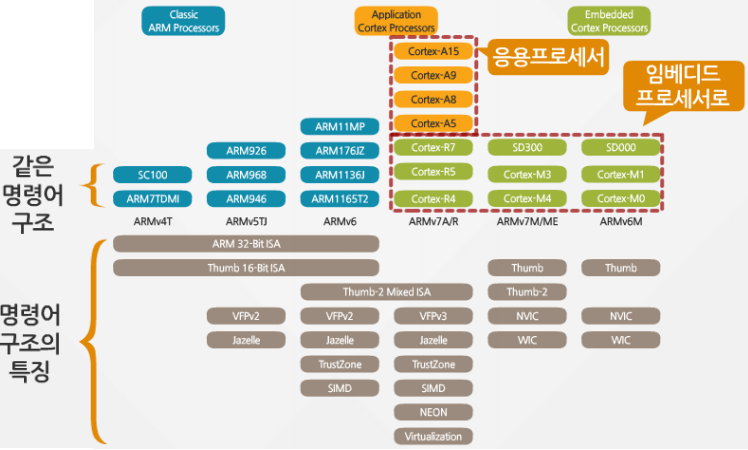

4) ARM 코어 로드맵

- 클래식 ARMCore

- Coretex 암코어 : 응용 프로세서용, 임베디드용

- 각 프로세서 군의 특성을 파악 -> 설계 목표에 부합하는 프로세서 선정

- 최신 프로세서 구조의 발전 흐름을 알아볼 수 있음

* VFP 부동소수점 고속 연산

* Jazelie 자바 명령어 가속

5) ARM 프로세서 요약

- ARM 7 패밀리 ; 명령어 v4T

- 3-state pipeline

코어끝 접미어 의미

- 코어가 제공하는 기능

- ARM7TDMI-S 예시

T = Thumb 명령어 지원

D = 디버그 인터페이스

M = 64비트 곱셈기

I = In-circuit 애뮬레이터 인터페이스

-S = 하드웨어 기술언어로 작성된 프로세서 코어, 자동 합성도구로 합성 가능

ARM 9 패밀리

- v4T 명령어

- 5-state pipeline, cache 사용

- Jazelle DBX 자바 가속 제공

- Havard 구조

ARM9E 패밀리

- ARM9 패밀리에 신호처리 명령어를 추가

- TCM : 빈번히 사용하는 데이터 엑세스 속도 향상 -> 실시간 향상

ARM10 패밀리

- 6state pipeline

- 64비트 명령어 처리, 부동 벡터 처리 명령 지원 VFP

- Jazelle DBX 자바 가속 제공

ARM11 패밀리

- 내부는 64비트, 외부는 32비트

- SIMD, TrustZone, Thumb-2 명령어 지원

- 멀티 코어 구성

Cortex 패밀리 (2004년부터 발표)

- A 시리즈 : 고성능 멀티미디어용

- R 시리즈 : 실시간 제어 임베디드용

- M 시리즈 : 저가격 마이크로 컨트롤러용

(2) ARM 명령어 구성

1) ARM ISA

2) Thumb 명령어

3) DSP 확장 명령어

4) 기타 확장 기능

1) ARM ISA

ARM ISA 특징

- 32비트 고정길이 명령어 : ARM 명령어

- 16비트 고정 길이 명령어 : Thumb 명령어

- 모든 명령어들이 조건부 명령어 -> 불만족시 실행 불가

- 하나의 명령어로 Shift와 ALU 연산 동시실행

- 명령어에 자동 증가/감소 모드 제공

- 여러 레지스터들을 동시에 메모리에 저장 및 로딩

=> 최대 15번 동시 읽기/쓰기 가능

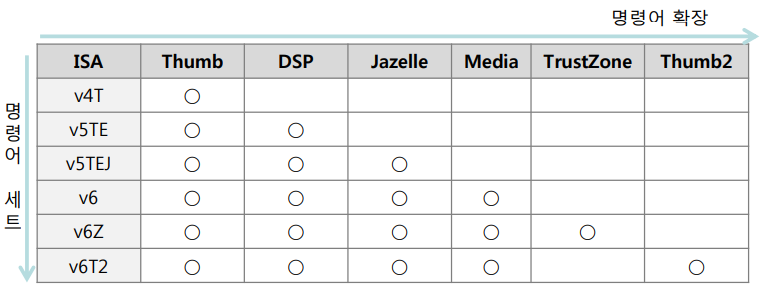

ARM ISA 확장

- 세로축 명령어 세트별. 가로축 명령어 확장기능

- T Thumb mode : 16비트 명령어 모드. 32비트 명령어를 16비트로 재배치 -> 메모리 사용량 줄이며, 메모리 인터페이스 부담 줄임

- DSP : 해당 명령어 셋이 DSP 제공

- Z Jazelle : 자바 하드웨어로 실행

- M Mdeia: 멀티미디어 데이터 처리를 위한 명령어 확장

- Z Trust Zone : 보안 관련

- T2 Thumb2 : Thumb 보다 축소된 명령어 기법 사용

- 명령어 셋 v4T : 버전 4 명령어 + Thumb 명령어

- v5TE : v4TE + DSP

2) Thumb 명령어

Thumb 16비트 명령어

- 프로그램 코드 크기 절약

- 외부 메모리 인터페이스 최소화 -> 소비전력 절약

ARM 명령어와 Thumb 명령어 비교

- 약 30% 프로그램 메모리 절약

- Thumb 모드 사용시 외부 메모리 소비전력 30% 절약

Thumb 명령어 단점

- 조건부 명령어 사용불가

- 명령어 내 상수 표현범위가 좁음

- 사용가능한 레지스터 범위가 R0 ~ R7으로 제한

ARM/Thumb 연동

- ARM State : ARM 명령어를 쓸수있는상태

- Thumb state : Thumb 명령어를 실행할수있는 상태

- BX 명령어로 전환 가능

- 프로세서 동작상태는 CPSR의 T 비트로 확인

3) DSP 확장 명령어

- CLZ(Count Leading Zero) 명령어 : MSB에서 LSB 검사하면서, 처음으로 1이 나타나는 비트위치 검색

- Saturate 연산 명령어 : 연산 결과가 표현 범위를 초과했는지 확인. 초과시 CPSR의 Q플래그 SET

- Signed Multiplication 지원

- Signed MAC 지원

- Double word load/store : 64비트 로드스토어를 LDRD, STRD 명령어로 표현

4) 확장 명령어

- Jazelle : BJX(자바 실행 전환) 명령 사용 -> 자바 바이트 코드 실행 속도 향상

- Media : SIMD 명령어로 오디오 비디오 처리 능력 향상 2~4배.

- Thumb2 : Thumb 명령어 셋 확장. 16비트 명령어보다 25% 빠름. 32비트 명령어보다 메모리 공간 절약

- TrustZone : 시스템 보안 강화

- VFP(Vector Floating Point) : 부동 소수점 연산

- NEON : 멀티미디어 데이터, 신호처리가 필요한 응용프로그램 성능 향상

'컴퓨터과학 > 임베디드' 카테고리의 다른 글

| ARM을 활용한 임베디드 시스템 설계 6 - 레지스터 (0) | 2020.05.04 |

|---|---|

| ARM을 활용한 임베디드 시스템 설계 5 - 메모리 (0) | 2020.05.03 |

| ARM을 활용한 임베디드 시스템 설계 3 - 개발 (0) | 2020.05.03 |

| ARM을 활용한 임베디드 시스템 설계 2 - 구성 (0) | 2020.05.03 |

| ARM을 활용한 임베디드 시스템 설계 1 - 개요 (0) | 2020.05.03 |